# Section 7 Wait-State Controller

#### 7.1 Overview

To simplify interfacing to low-speed external devices, the H8/532 has an on-chip wait-state controller (WSC) that can insert wait states (TW) to prolong bus cycles.

The wait-state function can be used in CPU and DTC access cycles to external addresses. It is not used in access to on-chip supporting modules. The Tw states are inserted between the T2 state and T3 state in the bus cycle. The number of wait states can be selected by a value set in the wait-state control register (WCR), or by holding the WAIT pin Low for the required interval.

#### 7.1.1 Features

The main features of the wait-state controller are:

- Selection of three operating modes

Programmable wait mode, pin wait mode, or pin auto-wait mode

- 0, 1, 2, or 3 wait states can be inserted.

And in the pin wait mode, 4 or more states can be inserted by holding the WAIT pin Low.

## 7.1.2 Block Diagram

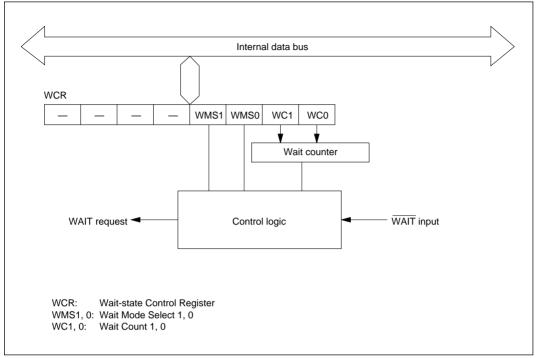

Figure 7-1 shows a block diagram of the wait-state controller.

Figure 7-1 Block Diagram of Wait-State Controller

## 7.1.3 Register Configuration

The wait-state controller has one control register: the wait-state control register described in table 7-1.

**Table 7-1 Register Configuration**

| Name                        | Abbreviation | Read/Write | Initial Value | Address |

|-----------------------------|--------------|------------|---------------|---------|

| Wait-state control register | WCR          | R/W        | H'F3          | H'FFF8  |

## 7.2 Wait-State Control Register

The wait-state control register (WCR) is an 8-bit register that specifies the wait mode and the number of wait states to be inserted. A reset initializes the WCR to specify the programmable wait mode with three wait states. The WCR is not initialized in the software standby mode.

| Bit           | 7 | 6 | 5 | 4 | 3    | 2    | 1   | 0   |

|---------------|---|---|---|---|------|------|-----|-----|

|               | _ | _ | _ |   | WMS1 | WMS0 | WC1 | WC0 |

| Initial value | 1 | 1 | 1 | 1 | 0    | 0    | 1   | 1   |

| Read/Write    | _ | _ | _ | _ | R/W  | R/W  | R/W | R/W |

Bits 7 to 4—Reserved: These bits cannot be modified and are always read as "1."

Bits 3 and 2—Wait Mode Select 1 and 0 (WMS1 and WMS0): These bits select the wait mode as shown below.

| Bit 3 | Bit 2 |                                                            |

|-------|-------|------------------------------------------------------------|

| WMS1  | WMS0  | Description                                                |

| 0     | 0     | Programmable wait mode (Initial value)                     |

| 0     | 1     | No wait states are inserted, regardless of the wait count. |

| 1     | 0     | Pin wait mode                                              |

| 1     | 1     | Pin auto-wait mode                                         |

Bits 1 and 0—Wait Count (WC1 and WC0): These bits specify the number of wait states to be inserted.

Wait states are inserted only in bus cycles in which the CPU or DTC accesses an external address.

| Bit 1 | Bit 0 |                                                       |

|-------|-------|-------------------------------------------------------|

| WC1   | WC0   | Description                                           |

| 0     | 0     | No wait states are inserted, except in pin wait mode. |

| 0     | 1     | 1 Wait state in inserted.                             |

| 1     | 0     | 2 Wait states are inserted.                           |

| 1     | 1     | 3 Wait states are inserted. (Initial value)           |

# 7.3 Operation in Each Wait Mode

Table 7-2 summarizes the operation of the three wait modes.

**Table 7-2 Wait Modes**

| Mode                                              | WAIT Pin Function | Insertion<br>Conditions                                          | Number of Wait<br>States Inserted                                                                                              |

|---------------------------------------------------|-------------------|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| Programmable wait mode WMS1 = "0" WMS0 = "0"      | Disabled          | Inserted on access to an off-chip address                        | 1 to 3 wait states are inserted, as specified by bits WC0 and WC1.                                                             |

| Pin wait mode<br>WMS1 = "1"<br>WMS0 = "0"         | Enabled           | Inserted on access to an off-chip address                        | 0 to 3 wait states are inserted, as specified by bits WC0 and WC1, plus additional wait states while the WAIT pin is held Low. |

| Pin auto-wait<br>mode<br>WMS1 = "1"<br>WMS0 = "1" | Enabled           | Inserted on access to an off-chip address if the WAIT pin is Low | 1 to 3 wait states are inserted, as specified by bits WC0 and WC1.                                                             |

### 7.3.1 Programmable Wait Mode

The programmable wait mode is selected when WMS1 = "0" and WMS0 = "0."

Whenever the CPU or DTC accesses an off-chip address, the number of wait states set in bits WC1 and WC0 are inserted. The  $\overline{\text{WAIT}}$  pin is not used for wait control; it is available as an I/O pin.

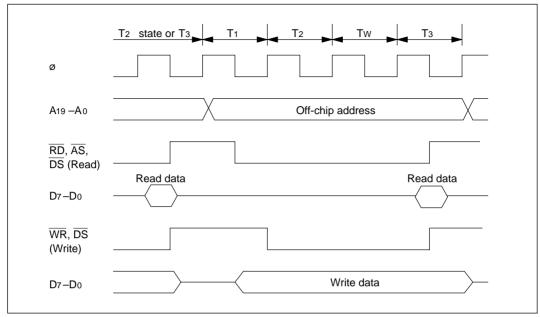

Figure 7-2 shows the timing of the operation in this mode when the wait count is 1 (WC1 = "0," WC0 = "1").

Figure 7-2 Programmable Wait Mode

#### 7.3.2 Pin Wait Mode

The pin wait mode is selected when WMS1 = "1" and WMS0 = "0."

In this mode the  $\overline{\text{WAIT}}$  function of the P14 / $\overline{\text{WAIT}}$  pin is used automatically.

The number of wait states indicated by bits WC1 and WC0 are inserted into any bus cycle in which the CPU or DTC accesses an off-chip address. In addition, wait states continue to be inserted as long as the  $\overline{\text{WAIT}}$  pin is held low. In particular, if the wait count is 0 but the  $\overline{\text{WAIT}}$  pin is Low at the rising edge of the  $\emptyset$  clock in the T2 state, wait states are inserted until the  $\overline{\text{WAIT}}$  pin goes High.

This mode is useful for inserting four or more wait states, or when different external devices require different numbers of wait states.

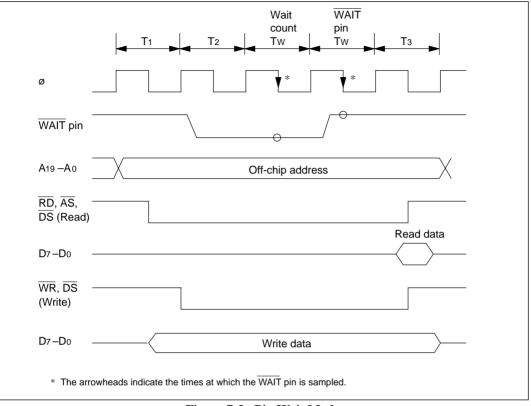

Figure 7-3 shows the timing of the operation in this mode when the wait count is 1 (WC1 = "0," WC0 = "1") and the  $\overline{\text{WAIT}}$  pin is held Low to insert one additional wait state.

Figure 7-3 Pin Wait Mode

#### 7.3.3 Pin Auto-Wait Mode

The pin auto-wait mode is selected when WMS1 = "1" and WMS0 = "1."

In this mode the  $\overline{\text{WAIT}}$  function of the P14 / $\overline{\text{WAIT}}$  pin is used automatically.

In this mode, the number of wait states indicated by bits WC1 and WC0 are inserted, but only if there is a Low input at the  $\overline{\text{WAIT}}$  pin.

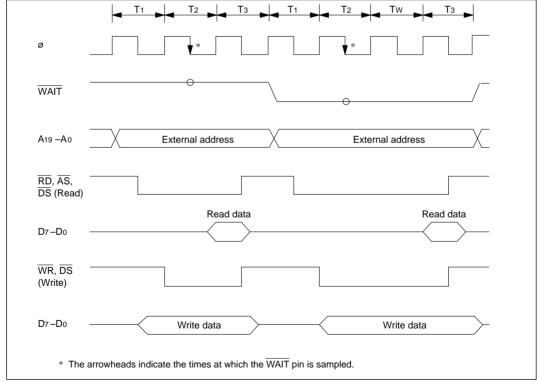

Figure 7-4 shows the timing of this operation when the wait count is 1.

In the pin auto-wait mode, the  $\overline{WAIT}$  pin is sampled only once, on the falling edge of the  $\emptyset$  clock in the T2 state. If the  $\overline{WAIT}$  pin is Low at this time, the wait-state controller inserts the number of wait states indicated by bits WC1 and WC0. The  $\overline{WAIT}$  pin is not sampled during the Tw and T3 states, so no additional wait states are inserted even if the  $\overline{WAIT}$  pin continues to be held Low.

This mode offers a simple way to interface a low-speed device: the wait states can be inserted by routing an address decode signal to the  $\overline{\text{WAIT}}$  pin.

Figure 7-4 Pin Auto-Wait Mode