# Appendix E Pin State

## E.1 Port State of Each Pin State

#### Table E-1 Port State

|                                                |      |        | Hardware |              |              |              |                          |

|------------------------------------------------|------|--------|----------|--------------|--------------|--------------|--------------------------|

| Port                                           |      |        | Standby  | Software     |              | Bus-right    | Program Execution        |

| Pin Name                                       | Mode | Reset  | Mode     | Standby mode | Sleep Mode   | Release Mode | State (Normal Operation) |

| P17 to P12                                     | 1    |        |          |              |              |              | Input/Output port or     |

| TMO, IRQ1, IRQ0                                | 2    |        |          |              |              |              | Control signal Input/    |

| WAIT, BREQ,                                    | 3    | Т      | Т        | keep*1       | keep*3       | keep*4       | Output                   |

| BACK                                           | 4    |        |          |              |              |              |                          |

|                                                | 7    |        |          | keep*2       | keep         |              | Input/Output port        |

| P11/E                                          | 1    |        |          | (DDR = 1)    | (DDR = 1)    | (DDR = 1)    | (DDR = 1)                |

| P10/ø                                          | 2    | Clock  |          | ø = H        | Clock output | Clock output | Clock output             |

|                                                | 3    | output | Т        | E = L        | (DDR = 0)    | (DDR = 0)    | (DDR = 0)                |

|                                                | 4    |        |          | (DDR = 0)    | т            | Т            | Input port               |

|                                                | 7    |        |          | Т            |              |              |                          |

| P24 to P20                                     | 1    |        |          |              |              |              | WR, RD, DS,              |

| $\overline{WR}, \overline{RD}, \overline{DS},$ | 2    | Н      |          | т            | н            | Т            | R/W, AS                  |

| R/W, AS                                        | 3    |        |          |              |              |              |                          |

|                                                | 4    |        |          |              |              |              |                          |

|                                                | 7    | Т      |          | keep         | keep         |              | Input/Output port        |

| P37 to P30                                     | 1    |        |          |              |              |              |                          |

| D7 to D0                                       | 2    |        |          | Т            | т            | Т            | D7 to Do                 |

|                                                | 3    | Т      | Т        |              |              |              |                          |

|                                                | 4    |        |          |              |              |              |                          |

|                                                | 7    |        |          | keep         | keep         |              | Input/Output port        |

| P47 to P40                                     | 1    |        |          |              |              |              |                          |

| A7 to A0                                       | 2    | L      |          | Т            | L            | Т            | A7 to A0                 |

|                                                | 3    |        | Т        |              |              |              |                          |

|                                                | 4    |        |          |              |              |              |                          |

|                                                | 7    | Т      |          | keep         | keep         |              | Input/Output port        |

| P57 to P50                                     | 1    | L      |          | Т            | L            | Τ'           | A15 to A8                |

| A15 to A8                                      | 2    | Т      |          | T*6          | *5           | T*6          | Address/Input port       |

|                                                | 3    | L      | Т        | Т            | L            | Т            | A15 to A8                |

|                                                | 4    | Т      |          | T*6          | *5           | T*6          | Address/Input port       |

|                                                | 7    |        |          | keep         | keep         |              | Input/Output port        |

| Port<br>Pin Name | Mode | Reset | Hardware<br>Standby<br>Mode | Software<br>Standby mode | Sleep Mode | Bus-right<br>Release Mode | Program Execution<br>State (Normal Operation) |

|------------------|------|-------|-----------------------------|--------------------------|------------|---------------------------|-----------------------------------------------|

| P63 to P60       | 1    | Reset | INIOUE                      | Standby mode             | Sleep Wode | Release Mode              |                                               |

| A19 to A16       | 2    | т     |                             | keep                     | keep       | keep                      | Input/Output port                             |

|                  | 3    | L     | Т                           | Т                        | L          | т                         | A19 to A16                                    |

|                  | 4    | Т     |                             | T*6                      | *5         | T*6                       | Address/Input port                            |

|                  | 7    |       |                             | keep                     | keep       |                           | Input/Output port                             |

| P77 to P70       | 1    |       |                             |                          |            |                           |                                               |

|                  | 2    |       |                             |                          |            |                           |                                               |

|                  | 3    | Т     | Т                           | keep*2                   | keep       | keep                      | Input port                                    |

|                  | 4    |       |                             |                          |            |                           |                                               |

|                  | 7    |       |                             |                          |            |                           |                                               |

| P87 to P80       | 1    |       |                             |                          |            |                           |                                               |

|                  | 2    |       |                             |                          |            |                           |                                               |

|                  | 3    | Т     | Т                           | Т                        | т          | Т                         | Input port                                    |

|                  | 4    |       |                             |                          |            |                           |                                               |

|                  | 7    |       |                             |                          |            |                           |                                               |

| P97 to P90       | 1    |       |                             |                          |            |                           |                                               |

|                  | 2    |       |                             |                          |            |                           |                                               |

|                  | 3    | Т     | Т                           | keep*2                   | keep       | keep                      | Input/Output port                             |

|                  | 4    |       |                             |                          |            |                           |                                               |

|                  | 7    |       |                             |                          |            |                           |                                               |

#### Table E-1 Port State (cont)

H: "High" = High level

L: "Low" = Low level

T: High Impedance

keep: If DDR = 0 and DR = 1 in port 5 and 6, Pull-up MOS holds on-state.

#### Notes:

- \*1 8 Bit Timer is reset, so P17 becomes input or output port controlled by DDR and DR. Also P12 goes to the high impedance state when it is programmed as BACK output.

- \*2 On-chip supporting modules are reset. So these pins become input or output ports controlled by DDR and DR.

- \*3  $\overline{\text{BREQ}}$  can be accepted and  $\overline{\text{BACK}}$  goes LOW.

- \*4 BACK outputs LOW.

- \*5 The pins programmed as address bus output LOW and others programmed as input are at the high impedance state.

If DDR = 0 and DR = 1, the pull-up MOS's keep ON state.

\*6 If DDR = 0 and DR = 1, the pull-up MOS's keep ON state.

| Port       | Mode | Reset | Hardware Standby Mode | Other Operating State* |

|------------|------|-------|-----------------------|------------------------|

| P57 to P50 | 1    | OFF   | OFF                   | OFF                    |

| A15 to A8  | 2    |       |                       | ON/OFF                 |

|            | 3    |       |                       | OFF                    |

|            | 4    |       |                       | ON/OFF                 |

|            | 7    |       |                       |                        |

| P57 to P50 | 1    | OFF   | OFF                   | ON/OFF                 |

| A15 to A8  | 2    |       |                       |                        |

|            | 3    |       |                       | OFF                    |

|            | 4    |       |                       | ON/OFF                 |

|            | 7    |       |                       |                        |

Table E-2Pull-Up MOS State

OFF: Pull-up MOS is always OFF.

ON/OFF: Pull-up MOS holds on-state only when DDR = "0" and DR = 1.

\* Including Software Standby Mode

### E.2 Pin Status in the Reset State

#### 1. Mode 1

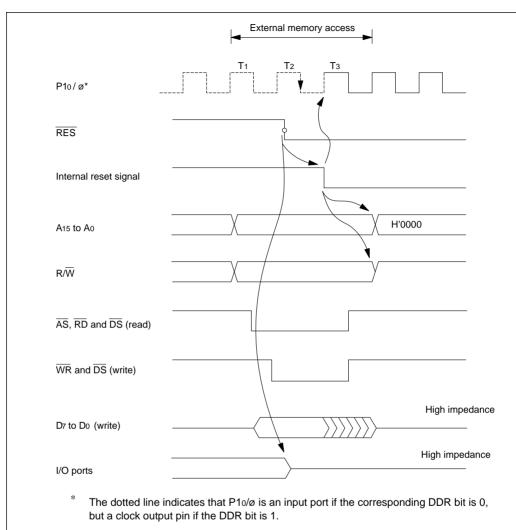

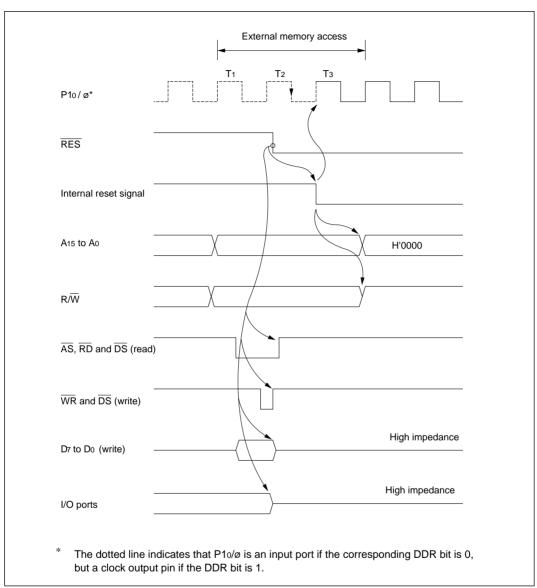

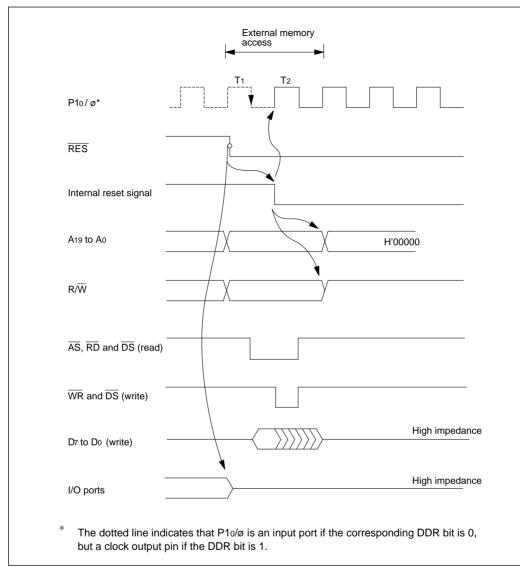

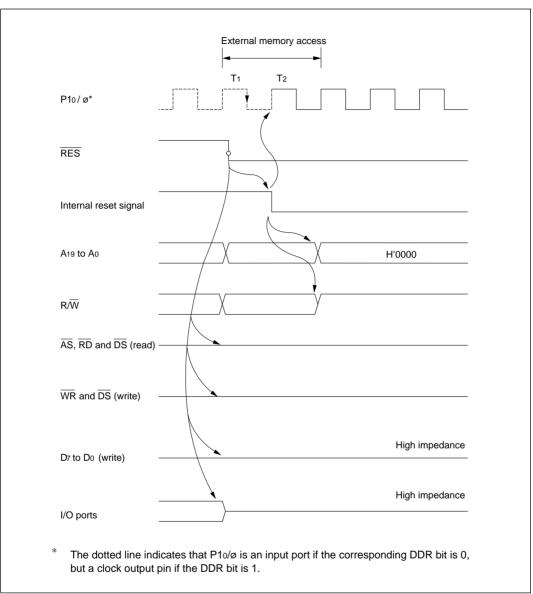

Figures E-1 and E-2 show how the pin states change when the  $\overline{\text{RES}}$  pin goes Low during external memory access in mode 1.

As soon as  $\overline{\text{RES}}$  goes Low, all ports are initialized to the input (high-impedance) state. The  $\overline{\text{AS}}$ ,  $\overline{\text{DS}}$ ,  $\overline{\text{RD}}$ , and  $\overline{\text{WR}}$  signals all go High. The data bus (D7 to D0) is placed in the high-impedance state.

The address bus and the  $R/\overline{W}$  signal are initialized 1.5 ø clock periods after the Low state of the  $\overline{RES}$  pin is sampled. All address bus signals are made Low. The  $R/\overline{W}$  signal is made High.

#### **ZTAT Versions**

Figure E-1 Reset during Memory Access (Mode 1)

Figure E-2 Reset during Memory Access (Mode 1)

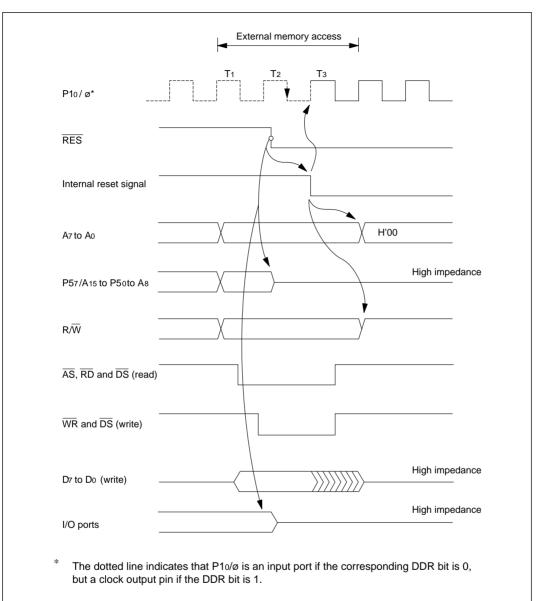

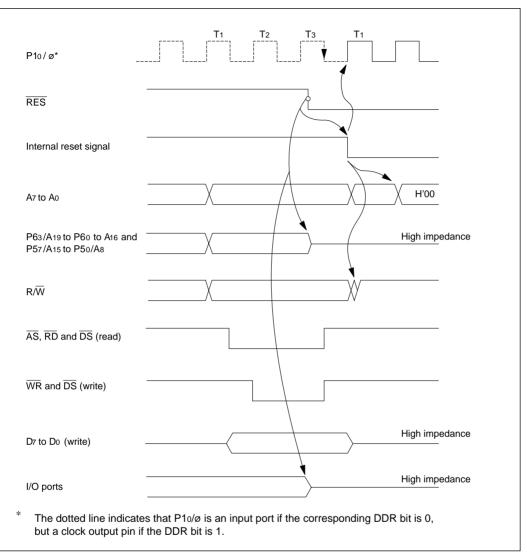

Figures E-3 and E-4 show how the pin states change when the  $\overline{\text{RES}}$  pin goes Low during external memory access in mode 2.

As soon as  $\overline{\text{RES}}$  goes Low, all ports are initialized to the input (high-impedance) state. The  $\overline{\text{AS}}$ ,  $\overline{\text{DS}}$ ,  $\overline{\text{RD}}$ , and  $\overline{\text{WR}}$  signals all go High. The data bus (D7 to D0) is placed in the high-impedance state. Pins P57/A15 to P50/A8 of the address bus are initialized as input ports.

Pins A7 to A0 of the address bus and the  $R/\overline{W}$  signal are initialized 1.5  $\phi$  clock periods after the Low state of the  $\overline{RES}$  pin is sampled. Pins A7 to A0 are made Low. The signal is made High.

Figure E-3 Reset during Memory Access (Mode 2)

#### **Masked-ROM Versions**

Figure E-4 Reset during Memory Access (Mode 2)

Figures E-5 and E-6 show how the pin states change when the  $\overline{\text{RES}}$  pin goes Low during external memory access in mode 3.

As soon as  $\overline{\text{RES}}$  goes Low, all ports are initialized to the input (high-impedance) state. The  $\overline{\text{AS}}$ ,  $\overline{\text{DS}}$ ,  $\overline{\text{RD}}$ , and  $\overline{\text{WR}}$  signals all go High. The data bus (D7 to D0) is placed in the high-impedance state.

The address bus and the signal are initialized 1.5  $\phi$  clock periods after the Low state of the  $\overline{\text{RES}}$  pin is sampled. All address bus signals are made Low. The R/W signal is made High.

#### **ZTAT Version**

Figure E-5 Reset during Memory Access (Mode 3)

Figure E-6 Reset during Memory Access (Mode 3)

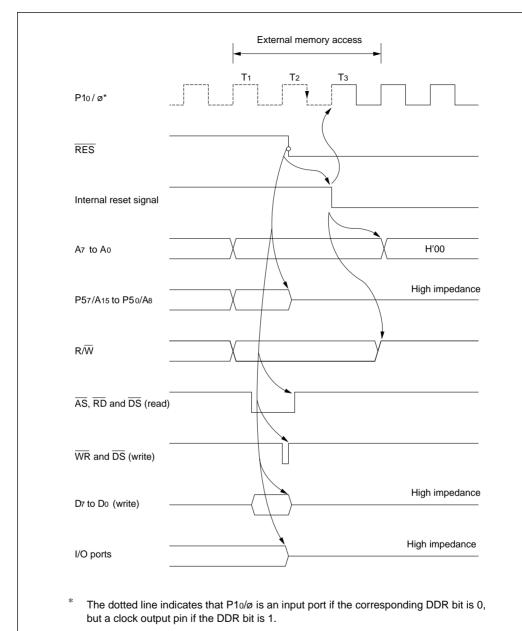

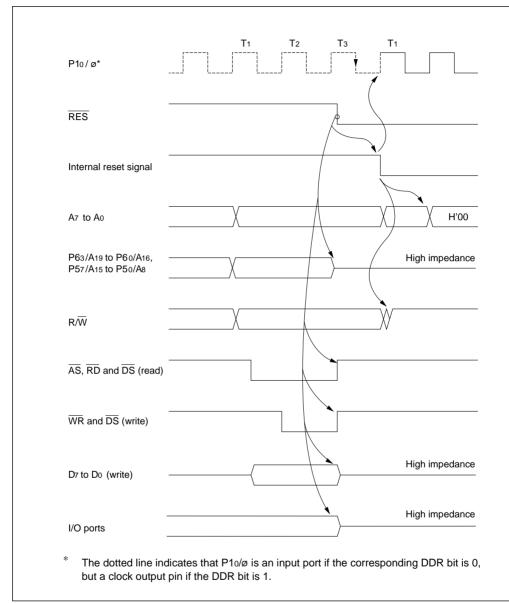

Figures E-7 and E-8 show how the pin states change when the  $\overline{\text{RES}}$  pin goes Low during external memory access in mode 4.

As soon as  $\overline{\text{RES}}$  goes Low, all ports are initialized to the input (high-impedance) state. The  $\overline{\text{AS}}$ ,  $\overline{\text{DS}}$ ,  $\overline{\text{RD}}$ , and  $\overline{\text{WR}}$  signals all go High. The data bus (D7 to D0) is placed in the high-impedance state. Pins P57/A15 to P50/A8 of the address bus and pins P63/A19 to P60/A16 of the page address bus are initialized as input ports.

Pins A7 to A0 of the address bus and the  $R/\overline{W}$  signal are initialized 1.5 ø clock periods after the Low state of the  $\overline{RES}$  pin is sampled. Pins A7 to A0 are made Low. The  $R/\overline{W}$  signal is made High.

#### **ZTAT Versions**

Figure E-7 Reset during Memory Access (Mode 4)

#### **Masked-ROM Versions**

Figure E-8 Reset during Memory Access (Mode 4)

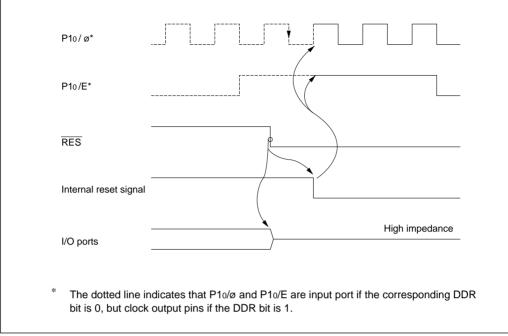

Figures E-9 and E-10 show how the pin states change when the  $\overline{\text{RES}}$  pin goes Low in mode 7.

As soon as RES goes Low, all ports are initialized to the input (high-impedance) state.

The clock output pins P10/ $\phi$  and P11/E are initialized 0.5  $\phi$  clock periods after the Low state of the RES pin is sampled. Both pins are initialized to the output state.

# P10/ Ø\* P10/ E\* RES Internal reset signal I/O ports The dotted line indicates that P10/Ø and P10/E are input port if the corresponding DDR bit is 0, but clock output pins if the DDR bit is 1.

#### ZTAT Versions

Figure E-9 Reset during Memory Access (Mode 7)

#### **Masked-ROM Versions**

Figure E-10 Reset during Memory Access (Mode 7)