## Section 9 I/O Ports

## 9.1 Overview

The H8/532 has nine ports. Ports 1, 3, 4, 5, 7, and 9 are eight-bit input/output ports. Port 2 is a five-bit input/output port. Port 6 is a four-bit input/output port. Port 8 is an eight-bit input-only port. Table 9-1 summarizes the functions of each port.

Input and output are memory-mapped. The CPU views each port as a data register (DR) located in the register field at the high end of page 0 of the address space. Each port (except port 8) also has a data direction register (DDR) which determines which pins are used for input and which for output. Port 1 has an additional control register (P1CR) for enabling and disabling IRQ0 and IRQ1 and setting other controls.

To read data from an I/O port, the CPU selects input in the data direction register and reads the data register. This causes the input logic level at the pin to be placed directly on the internal data bus. There is no intervening input latch.

To send data to an output port, the CPU selects output in the data direction register and writes the desired data in the data register, causing the data to be held in a latch. The latch output drives the pin through a buffer amplifier. If the CPU reads the data register of an output port, it obtains the data held in the latch rather than the actual level of the pin.

As table 9-1 indicates, all of the I/O port pins have dual functions. For example, pin 7 of port 1 can be used either as a general-purpose I/O pin (P17), or for output of the TMO signal from the on-chip 8-bit timer. The function is determined by the MCU operating mode, or by a value set in a control register.

Outputs from ports 1 to 6 can drive one TTL load and a 90pF capacitive load. Outputs from ports 7 and 9 can drive one TTL load and a 30pF capacitive load.

Outputs from ports 1 to 7 and 9 can also drive a Darlington transistor pair. Outputs from port 4 can drive a light-emitting diode (with 10mA current sink). Ports 5 and 6 have built-in MOS pull-ups for each input. Port 7 has Schmitt inputs.

Schematic diagrams of the I/O port circuits are shown in appendix C.

## Table 9-1 Input/Output Port Summary

| Port   | Description        | Pins        | Mode 1     | •                 | ed Mode<br>Mode 3 |                | Single-Chip Mode<br>(Mode 7) |

|--------|--------------------|-------------|------------|-------------------|-------------------|----------------|------------------------------|

| Port 1 | 8-Bit input/output | P17 / TMO   | These in   | put/outpu         | t pins dou        | uble as and    | <u> </u>                     |

|        |                    | P16 / IRQ1  |            | nd as IRQ         |                   |                |                              |

|        |                    | P15 / IRQ0  | •          | in (TMO) i        |                   | •              |                              |

|        |                    | P14 / WAIT  |            |                   |                   | T, BREQ,       | Input/output                 |

|        |                    | P13 / BREQ  | and BAC    | K when r          | necessary         | control-       | port                         |

|        |                    | P12 / BACK  | register l | bits are se       | et to "1."        |                |                              |

|        |                    | P11/E       | These pi   | ins functio       | on as inpu        | It pins or as  |                              |

|        |                    | P10/ø       | -          |                   | =                 | pending on     |                              |

|        |                    |             | -          | direction         | -                 | -              |                              |

| Port 2 | 5-Bit input/output | P24 / WR    | Bus cont   | trol signal       | outputs           |                | Input/output                 |

|        | port               | P23 / RD    | (WR, RD    | , <u>D</u> S, R/V | V, AS)            |                | port                         |

|        |                    | P22 / DS    | •          |                   |                   |                |                              |

|        |                    | P21 / R/W   |            |                   |                   |                |                              |

|        |                    | P20 / AS    |            |                   |                   |                |                              |

| Port 3 | 8-Bit input/output | P37 - P30 / | Data bus   | s (D7 – Do        | )                 |                | Input/output                 |

|        | port               | D7 – D0     |            |                   |                   |                | port                         |

| Port 4 | 8-Bit input/output | P47 – P40 / | Low add    | ress bits         | (A7 – A0)         |                | Input/output                 |

|        | port               | A7 – A0     |            |                   |                   |                | port                         |

|        | Can drive a LED    |             |            |                   |                   |                |                              |

| Port 5 | 8-Bit input/output | P57 – P50 / | High       | High              | High              | High           | Input/output                 |

|        | port               | A15 – A8    | address    | address           | address           | address        | port                         |

|        | Built-in input     |             | bus        | bus if            | bus               | bus if         |                              |

|        | pull-up (MOS)      |             | (A15 –     | DDR is            | (A15 –            | DDR is         |                              |

|        |                    |             | A8)        | set to "1'        | ' A8)             | set to "1"     |                              |

| Port 6 | 4-Bit input/output | P63-P60/    | Input/out  | tput port         | Page              | Page           | Input/output                 |

|        | port               | A19 – A16   |            |                   | address           | address        | port                         |

|        | Built-in input     |             |            |                   | bus               | bus if DDR     |                              |

|        | pull-up (MOS)      |             |            |                   | (A19 –            | is set to "1," | 1                            |

|        |                    |             |            |                   | A16)              | input port if  |                              |

|        |                    |             |            |                   |                   | DDR is set     |                              |

|        |                    |             |            |                   |                   | to "0"         |                              |

|        |                    |               | Expanded Modes                           | Single-Chip Mode |

|--------|--------------------|---------------|------------------------------------------|------------------|

| Port   | Description        | Pins          | Mode 1 Mode 2 Mode 3 Mode 4              | (Mode 7)         |

| Port 7 | 8-Bit input/output | P77 / FTOA1   | Input/output for free-running timers 1,  |                  |

|        | port               | P76 / FTOB3 / | 2 and 3 (FTI1 to FTI3, FTCI1 to FTCI3,   |                  |

|        | (Schmitt inputs)   | FTCI3         | FTOB1 to FTOB3, FTOA1), input for        |                  |

|        |                    | P75 / FTOB2 / | 8-bit timer input (TMCI, TMRI), and 8-   | bit              |

|        |                    | FTCI2         | input/output port                        |                  |

|        |                    | P74 / FTOB1 / | (P77 to P70)                             |                  |

|        |                    | FTCI1 /       |                                          |                  |

|        |                    | P73 / FTI3    |                                          |                  |

|        |                    | TMRI          |                                          |                  |

|        |                    | P72 / FTI2    |                                          |                  |

|        |                    | P71 / FTI1    |                                          |                  |

|        |                    | P70 / TMCI    |                                          |                  |

| Port 8 | 8-Bit input port   | P80 - P87     | Analog input pins for A/D converter, and | nd               |

|        |                    | AN7 – AN0     | 8-bit input port                         |                  |

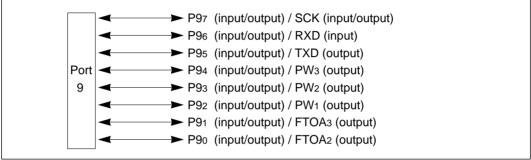

| Port 9 | 8-Bit input/output | P97 / SCK     | Output for free-running timers 2 and 3   |                  |

|        | port               | P96 / RXD     | (FTOA2, FTOA3), PWM timer output         |                  |

|        |                    | P95 / TXD     | (PW1, PW2, PW3), serial communication    | on               |

|        |                    | P94 / PW3     | interface (SCI) input/output (TXD, RXI   | D,               |

|        |                    | P93 / PW2     | SCK), and 8-bit input/output port        |                  |

|        |                    | P92 / PW1     |                                          |                  |

|        |                    | P91 / FTOA3   |                                          |                  |

|        |                    | P90 / FTOA2   |                                          |                  |

## Table 9-1 Input/Output Port Summary (cont)

## 9.2 Port 1

Г

## 9.2.1 Overview

Port 1 is an 8-bit input/output port with the pin configuration shown in figure 9-1. All pins have dual functions, except that in the single-chip mode pins 4, 3, and 2 do not have the WAIT, BREQ, and BACK functions. (because the CPU does not access an external bus.)

Outputs from port 1 can drive one TTL load and a 90pF capacitive load. They can also drive a Darlington transistor pair.

|      | Pin           | Expanded Modes                     | Single-Chip Mode                  |

|------|---------------|------------------------------------|-----------------------------------|

|      | 🗨 🕞 P17 / TMO | P17 (input/output) / TMO (output)  | P17 (input/output) / TMO (output) |

|      | ← P16 / IRQ1  | P16 (input/output) / IRQ1 (input)  | P16 (input/output) / IRQ1 (input) |

|      | ← P15 / IRQ0  | P15 (input/output) / IRQ0 (input)  | P15 (input/output) / IRQ0 (input) |

| Port | ← P14 / WAIT  | P14 (input/output) / WAIT (input)  | P14 (input/output)                |

| 1    | P13 / BREQ    | P13 (input/output) / BREQ (input)  | P13 (input/output)                |

|      | P12/BACK      | P12 (input/output) / BACK (output) | P12 (input/output)                |

|      | ← P11 / E     | P11 (input) / E (output)           | P11 (input) / E (output)          |

|      | P10/ø         | P10 (input) / ø (output)           | P10 (input) / ø (output)          |

|      |               |                                    |                                   |

#### Figure 9-1 Pin Functions of Port 1

#### 9.2.2 Port 1 Registers

**Register Configuration:** Table 9-2 lists the registers of port 1.

#### Table 9-2 Port 1 Registers

| Name                           | Abbreviation | Read/Write | Initial Value  | Address |

|--------------------------------|--------------|------------|----------------|---------|

| Port 1 data direction register | P1DDR        | W          | H'03           | H'FF80  |

| Port 1 data register           | P1DR         | R/W*1      | Undetermined*2 | H'FF82  |

| Port 1 control register        | P1CR         | R/W        | H'87           | H'FFFC  |

\*1 Bits 1 and 0 are read-only.

\*2 Bits 1 and 0 are undetermined. Other bits are initialized to "0."

#### 1. Port 1 Data Direction Register (P1DDR)—H'FF80

| Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|---------------|--------|--------|--------|--------|--------|--------|--------|--------|

|               | P17DDR | P16DDR | P1₅DDR | P14DDR | P13DDR | P12DDR | P11DDR | P10DDR |

| Initial value | 0      | 0      | 0      | 0      | 0      | 0      | 1      | 1      |

| Read/Write    | W      | W      | W      | W      | W      | W      | W      | W      |

P1DDR is an 8-bit register that selects the direction of each pin in port 1. A pin functions as an output pin if the corresponding bit in P1DDR is set to "1," and as an input pin if the bit is cleared to "0."

P1DDR can be written but not read. An attempt to read this register does not cause an error, but all bits are read as "1," regardless of their true values.

A reset initializes P1DDR to H'03, so that pins P11 and P10 carry clock outputs and the other pins are set for input. In the hardware standby mode, P1DDR is cleared to H'00, stopping the clock outputs. P1DDR is not initialized in the software standby mode, so if a P1DDR bit is set to "1" when the chip enters the software standby mode, the corresponding pin continues to output the value in the port 1 data register (or the ø or E clock).

#### 2. Port 1 Data Register (P1DR)—H'FF82

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|

|               | P17 | P16 | P15 | P14 | P13 | P12 | P11 | P10 |

| Initial value | 0   | 0   | 0   | 0   | 0   | 0   | _   |     |

| Read/Write    | R/W | R/W | R/W | R/W | R/W | R/W | R   | R   |

P1DR is an 8-bit register containing the data for pins P17 to P10. When the CPU reads P1DR, for output pins it reads the value in the P1DR latch, but for input pins, it obtains the pin status directly.

Note that when pins P11 and P10 are used for output, they output the clock signals ( $\emptyset$  and E), not the contents of P1DR. If the CPU reads P11 and P10 (when P11DDR = P10DDR = 1), it obtains the clock values at the current instant.

#### 3. Port 1 Control Register (P1CR)—H'FFFC

| Bit           | 7 | 6     | 5             | 4     | 3    | 2 | 1 | 0 |

|---------------|---|-------|---------------|-------|------|---|---|---|

|               | — | IRQ1E | <b>IRQ</b> 0E | NMIEG | BRLE | — | _ | _ |

| Initial value | 1 | 0     | 0             | 0     | 0    | 1 | 1 | 1 |

| Read/Write    | _ | R/W   | R/W           | R/W   | R/W  | _ | _ | _ |

P1CR selects the functions of four of the port 1 pins. It also selects the input edge of the NMI pin.

At a reset and in the hardware standby mode, P1CR is initialized to H'87. It is not initialized in the software standby mode.

Bit 7—Reserved: This bit cannot be modified and is always read as "1."

Bit 6—Interrupt Request 1 Enable (IRQ1E): This bit selects the function of pin P16.

| Bit 6 |                                                                 |                        |

|-------|-----------------------------------------------------------------|------------------------|

| IRQ1E | Description                                                     |                        |

| 0     | P16 functions as an input/output pin.                           | (Initial value)        |

| 1     | P16 functions as the IRQ1 input pin, regardless of the value se | t in P16DDR. (However, |

|       | the CPU can still read the pin status by reading P1DR.)         |                        |

Bit 5—Interrupt Request 0 Enable (IRQ0E): This bit selects the function of pin P15.

| Bit 5 |                                                                  |                        |

|-------|------------------------------------------------------------------|------------------------|

| IRQ₀E | Description                                                      |                        |

| 0     | P15 functions as an input/output pin.                            | (Initial value)        |

| 1     | P15 functions as the IRQ0 input pin, regardless of the value set | t in P15DDR. (However, |

|       | the CPU can still read the pin status by reading P1DR.)          |                        |

**Bit 4—Nonmaskable Interrupt Edge (NMIEG):** This bit selects the input edge of the NMI pin. It is not related to port 0.

| Bit 4 |                                                          |                 |

|-------|----------------------------------------------------------|-----------------|

| NMIEG | Description                                              |                 |

| 0     | A nonmaskable interrupt is generated on the falling edge | (Initial value) |

|       | of the input at the NMI pin.                             |                 |

| 1     | A nonmaskable interrupt is generated on the rising edge  |                 |

|       | of the input at the NMI pin.                             |                 |

**Bit 3—Bus Release Enable (BRLE):** This bit selects the functions of pins P12 and P13. It is valid only in the expanded modes (modes 1, 2, 3, and 4). In the single-chip mode, pins P12 and P13 function as input/output pins regardless of the value of the BRLE bit.

| Bit 3 |                                                                  |                 |

|-------|------------------------------------------------------------------|-----------------|

| BRLE  | Description                                                      |                 |

| 0     | P13 and P12 function as input/output pins.                       | (Initial value) |

| 1     | P13 functions as the input pin. P12 functions as the output pin. |                 |

Bits 2 to 0—Reserved: These bits cannot be modified and are always read as "1."

#### 9.2.3 Pin Functions in Each Mode

Port 1 operates differently in the expanded modes (modes 1, 2, 3, and 4) and the single-chip mode (mode 7). Table 9-3 explains how the pin functions are selected in the expanded mode. Table 9-4 explains how the pin functions are selected in the single-chip mode.

#### Table 9-3 Port 1 Pin Functions in Expanded Modes

#### Pin Functions and How they are Selected

P17 / TMO The function depends on output select bits 3 to 0 (OS3 to OS0) of the 8-bit timer control/status register (TCSR) and on the P17DDR bit as follows:

| OS3 to OS0   | All four bit | s are "0"  | At least one bit is "1" |   |  |

|--------------|--------------|------------|-------------------------|---|--|

| P17DDR       | 0            | 1          | 0                       | 1 |  |

| Pin function | P17 input    | P17 output | TMO output              |   |  |

P16 / IRQ1 The function depends on the IRQ1E bit and the P16DDR bit as follows:

| IRQ1E        | 0         |            | 1    |       |

|--------------|-----------|------------|------|-------|

| P16DDR       | 0 1       |            | 0    | 1     |

| Pin function | P16 input | P16 output | IRQ1 | input |

P15 / IRQ0 The function depends on the IRQ0E bit and the P15DDR bit as follows:

| IRQ0E        | 0         |            | 1            |       |

|--------------|-----------|------------|--------------|-------|

| P15DDR       | 0         | 1          | 0            | 1     |

| Pin function | P15 input | P15 output | <b>IRQ</b> 0 | input |

#### Table 9-3 Port 1 Pin Functions in Expanded Modes (cont)

## Pin Functions and How they are Selected P14 / WAIT The function depends on the wait mode select 1 bit (WMS1) of the wait-state control register (WCR) and the P14DDR bit as follows:

| WMS1         | 0         |            | 1    |       |

|--------------|-----------|------------|------|-------|

| P14DDR       | 0 1       |            | 0    | 1     |

| Pin function | P14 input | P14 output | WAIT | input |

P13 / BREQ The function depends on the BRLE bit and the P13DDR bit as follows:

| BRLE         | 0         |            | 1    |         |

|--------------|-----------|------------|------|---------|

| P13DDR       | 0         | 1          | 0    | 1       |

| Pin function | P13 input | P13 output | BREC | t input |

P12 / BACK The function depends on the BRLE bit and the P12DDR bit as follows:

| BRLE         | 0         |            | 1    |         |

|--------------|-----------|------------|------|---------|

| P12DDR       | 0 1       |            | 0    | 1       |

| Pin function | P12 input | P12 output | BACK | ( input |

P11/E

| P11DDR       | 0     | 1              |

|--------------|-------|----------------|

| Pin function | Input | E clock output |

P10/ø

| P10DDR       | 0     | 1              |

|--------------|-------|----------------|

| Pin function | Input | ø clock output |

## Table 9-4 Port 1 Pin Functions in Single-Chip Modes

#### Pin Selection of Pin Functions

P17 / TMO The function depends on output select bits 3 to 0 (OS3 to OS0) of the 8-bit timer control/status register (TCSR) and on the P17DDR bit as follows:

| OS3 to OS0   | All four bits are "0" |            | At least or | ne bit is "1" |

|--------------|-----------------------|------------|-------------|---------------|

| P17DDR       | 0                     | 1          | 0           | 1             |

| Pin function | P17 input             | P17 output | TMO         | output        |

P16 / IRQ1 The function depends on the IRQ1E bit and the P16DDR bit as follows:

| IRQ1E        | 0         |            | 1            |       |

|--------------|-----------|------------|--------------|-------|

| P16DDR       | 0 1       |            | 0            | 1     |

| Pin function | P16 input | P16 output | <b>IRQ</b> 1 | input |

P15 / IRQ0 The function depends on the IRQ0E bit and the P15DDR bit as follows:

| IRQ0E        | 0         |            | 1            |       |

|--------------|-----------|------------|--------------|-------|

| P15DDR       | 0         | 1          | 0            | 1     |

| Pin function | P15 input | P15 output | <b>IRQ</b> 0 | input |

P14

| P14DDR       | 0     | 1      |

|--------------|-------|--------|

| Pin function | Input | Output |

P13

| P13DDR       | 0     | 1      |

|--------------|-------|--------|

| Pin function | Input | Output |

#### Table 9-4 Port 1 Pin Functions in Single-Chip Modes (cont)

## Pin

**Selection of Pin Functions**

P12

| D4 DDD       | •     | 4      |

|--------------|-------|--------|

| P12DDR       | 0     | 1      |

| Pin function | Input | Output |

#### P11/E

| P11DDR       | 0     | 1              |

|--------------|-------|----------------|

| Pin function | Input | E clock output |

P10/ø

| P10DDR       | 0     | 1              |

|--------------|-------|----------------|

| Pin function | Input | ø clock output |

## 9.3 Port 2

#### 9.3.1 Overview

Port 2 is a five-bit input/output port with the pin configuration shown in figure 9-2. It functions as an input/output port only in the single-chip mode. In the expanded modes it is used for output of bus control signals.

Outputs from port 2 can drive one TTL load and a 90pF capacitive load. They can also drive a Darlington transistor pair.

|      | Pin                            | Expanded Modes | Single-Chip Mode   |

|------|--------------------------------|----------------|--------------------|

|      | ► P24 / WR                     | WR (output)    | P24 (input/output) |

| Port | ► P23 / RD                     | RD (output)    | P23 (input/output) |

| 2    | <ul> <li>► P22 / DS</li> </ul> | DS (output)    | P22 (input/output) |

|      | <->► P21 / R/W                 | R/W (output)   | P21 (input/output) |

|      | → P20 / AS                     | AS (output)    | P20 (input/output) |

| Figure 9-2 | Pin Functions | of Port 2 |

|------------|---------------|-----------|

|------------|---------------|-----------|

#### 9.3.2 Port 2 Registers

Register Configuration: Table 9-5 lists the registers of port 2.

#### Table 9-5Port 2 Registers

| Name                           | Abbreviation | Read/Write | Initial Value | Address |

|--------------------------------|--------------|------------|---------------|---------|

| Port 2 data direction register | P2DDR        | W          | H'E0          | H'FF81  |

| Port 2 data register           | P2DR         | R/W        | H'E0          | H'FF83  |

#### 1. Port 2 Data Direction Register (P2DDR)—H'FF81

| Bit           | 7 | 6 | 5 | 4      | 3      | 2      | 1      | 0      |

|---------------|---|---|---|--------|--------|--------|--------|--------|

|               | — | — | _ | P24DDR | P23DDR | P22DDR | P21DDR | P20DDR |

| Initial value | 1 | 1 | 1 | 0      | 0      | 0      | 0      | 0      |

| Read/Write    | _ | _ | _ | W      | W      | W      | W      | W      |

P2DDR is an 8-bit register that selects the direction of each pin in port 2.

**Single-Chip Mode:** A pin functions as an output pin if the corresponding bit in P2DDR is set to "1," and as an input pin if the bit is cleared to "0."

Bits 4 to 0 can be written but not read. An attempt to read this register does not cause an error, but all bits are read as "1," regardless of their true values.

Bits 7 to 5 are reserved. They cannot be modified and are always read as "1."

At a reset and in the hardware standby mode, P2DDR is initialized to H'E0, making all five pins input pins. P2DDR is not initialized in the software standby mode, so if a P2DDR bit is set to "1" when the chip enters the software standby mode, the corresponding pin continues to output the value in the port 2 data register.

**Expanded Modes:** All bits of P2DDR are fixed at "1" and cannot be modified.

#### 2. Port 2 Data Register (P2DR)-H'FF83

| Bit           | 7 | 6 | 5 | 4   | 3   | 2   | 1   | 0   |

|---------------|---|---|---|-----|-----|-----|-----|-----|

|               | — | — | _ | P24 | P23 | P22 | P21 | P20 |

| Initial value | 1 | 1 | 1 | 0   | 0   | 0   | 0   | 0   |

| Read/Write    | — | — | _ | R/W | R/W | R/W | R/W | R/W |

P2DR is an 8-bit register containing the data for pins P24 to P20.

Bits 7 to 5 are reserved. They cannot be modified and are always read as "1."

When the CPU reads P2DR, for output pins it reads the value in the P2DR latch, but for input pins, it obtains the pin status directly.

#### 9.3.3 Pin Functions in Each Mode

Port 2 has different functions in the expanded modes (modes 1, 2, 3, 4) and the single-chip mode (mode 7). Separate descriptions are given below.

**Pin Functions in Expanded Modes:** In the expanded modes (modes 1, 2, 3, and 4), all pins of P2DDR is automatically set to "1" for output. Port 2 outputs the bus control signals ( $\overline{AS}$ ,  $R/\overline{W}$ ,  $\overline{DS}$ ,  $\overline{RD}$ ,  $\overline{WR}$ ).

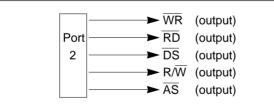

Figure 9-3 shows the pin functions in the expanded modes.

Figure 9-3 Port 2 Pin Functions in Expanded Modes

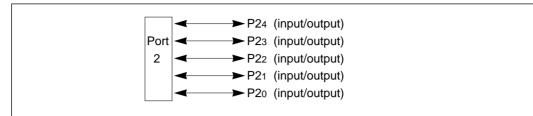

**Pin Functions in Single-Chip Mode:** In the single-chip mode (mode 7), each of the port 2 pins can be designated as an input pin or an output pin, as indicated in figure 9-4, by setting the corresponding bit in P2DDR to "1" for output or clearing it to "0" for input.

Figure 9-4 Port 2 Pin Functions in Single-Chip Mode

## 9.4 Port 3

#### 9.4.1 Overview

Port 3 is an 8-bit input/output port with the pin configuration shown in figure 9-5. In the expanded modes it operates as the external data bus (D7 - D0). In the single-chip mode it operates as a general-purpose input/output port.

Outputs from port 3 can drive one TTL load and a 90pF capacitive load. They can also drive a Darlington transistor pair.

|        | Pin        | Expanded Modes    | Single-Chip Mode   |

|--------|------------|-------------------|--------------------|

|        | P37 / D7   | D7 (input/output) | P37 (input/output) |

|        | ► P36 / D6 | D6 (input/output) | P36 (input/output) |

|        | ► P35 / D5 | D5 (input/output) | P35 (input/output) |

| Port < | ► P34 / D4 | D4 (input/output) | P34 (input/output) |

| 3 🗖    | ► P33 / D3 | D3 (input/output) | P33 (input/output) |

|        | ► P32 / D2 | D2 (input/output) | P32 (input/output) |

| -      | P31 / D1   | D1 (input/output) | P31 (input/output) |

| -      | ► P30 / D0 | Do (input/output) | P30 (input/output) |

Figure 9-5 Pin Functions of Port 3

#### 9.4.2 Port 3 Registers

Register Configuration: Table 9-6 lists the registers of port 3.

| Table 9 | 9-6 | Port 3 | 3 Reg | gisters |

|---------|-----|--------|-------|---------|

|---------|-----|--------|-------|---------|

| Name                           | Abbreviation | Read/Write | Initial Value | Address |

|--------------------------------|--------------|------------|---------------|---------|

| Port 3 data direction register | P3DDR        | W          | H'00          | H'FF84  |

| Port 3 data register           | P3DR         | R/W        | H'00          | H'FF86  |

#### 1. Port 3 Data Direction Register (P3DDR)—H'FF84

| Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|---------------|--------|--------|--------|--------|--------|--------|--------|--------|

|               | P37DDR | P36DDR | P3₅DDR | P34DDR | P33DDR | P32DDR | P31DDR | P30DDR |

| Initial value | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| Read/Write    | W      | W      | W      | W      | W      | W      | W      | W      |

P3DDR is an 8-bit register that selects the direction of each pin in port 3.

**Single-Chip Mode:** A pin functions as an output pin if the corresponding bit in P3DDR is set to "1," and as an input pin if the bit is cleared to "0."

P3DDR can be written but not read. An attempt to read this register does not cause an error, but all bits are read as "1," regardless of their true values.

At a reset and in the hardware standby mode, P3DDR is initialized to H'00, making all eight pins input pins. P3DDR is not initialized in the software standby mode, so if a P3DDR bit is set to "1" when the chip enters the software standby mode, the corresponding pin continues to output the value in the port 3 data register.

Expanded Modes: P3DDR is not used.

#### 2. Port 3 Data Register (P3DR)-H'FF86

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|

|               | P37 | P36 | P35 | P34 | P33 | P32 | P31 | P30 |

| Initial value | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| Read/Write    | R/W |

P3DR is an 8-bit register containing the data for pins P37 to P30.

At a reset and in the hardware standby mode, P3DR is initialized to H'00.

When the CPU reads P3DR, for output pins it reads the value in the P3DR latch, but for input pins, it obtains the pin status directly.

#### 9.4.3 Pin Functions in Each Mode

Port 3 has different functions in the expanded modes (modes 1, 2, 3, 4) and the single-chip mode (mode 7). Separate descriptions are given below.

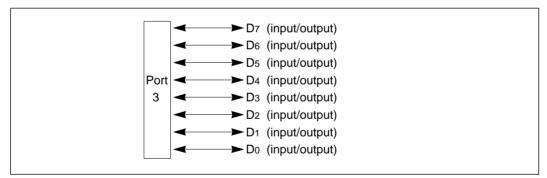

**Pin Functions in Expanded Modes:** In the expanded modes (modes 1, 2, 3, and 4), port 3 is automatically used as the data bus and P3DDR is ignored. Figure 9-6 shows the pin functions for the expanded modes.

Figure 9-6 Port 3 Pin Functions in Expanded Modes

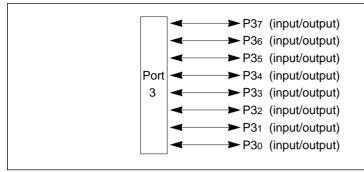

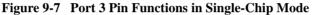

**Pin Functions in Single-Chip Mode:** In the single-chip mode (mode 7), each of the port 3 pins can be designated as an input pin or an output pin, as indicated in figure 9-7, by setting the corresponding bit in P3DDR to "1" for output or clearing it to "0" for input.

## 9.5 Port 4

#### 9.5.1 Overview

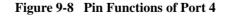

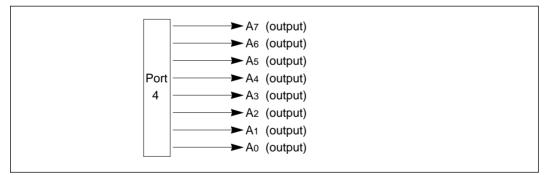

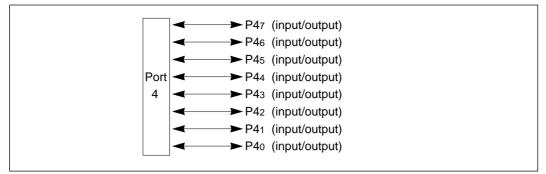

Port 4 is an 8-bit input/output port with the pin configuration shown in figure 9-8. In the expanded modes it provides the low bits (A7 - A0) of the address bus. In the single-chip mode it operates as a general-purpose input/output port.

Outputs from port 4 can drive one TTL load and a 90pF capacitive load. They can also drive a Darlington transistor pair or LED (with 8mA current sink).

|        | Pin        | Expanded Modes | Single-Chip Mode   |

|--------|------------|----------------|--------------------|

| -      | ► P47 / A7 | A7 (output)    | P47 (input/output) |

| -      | ► P46 / A6 | A6 (output)    | P46 (input/output) |

| -      | ► P45 / A5 | A5 (output)    | P45 (input/output) |

| Port 🗲 | ► P44 / A4 | A4 (output)    | P44 (input/output) |

| 4 🗲    | ► P43 / A3 | A3 (output)    | P43 (input/output) |

| -      | ► P42 / A2 | A2 (output)    | P42 (input/output) |

| -      | ► P41 / A1 | A1 (output)    | P41 (input/output) |

| -      | ► P40 / A0 | Ao (output)    | P40 (input/output) |

#### 9.5.2 Port 4 Registers

Register Configuration: Table 9-7 lists the registers of port 4.

#### Table 9-7Port 4 Registers

| Name                           | Abbreviation | Read/Write | Initial Value | Address |

|--------------------------------|--------------|------------|---------------|---------|

| Port 4 data direction register | P4DDR        | W          | H'00          | H'FF85  |

| Port 4 data register           | P4DR         | R/W        | H'00          | H'FF87  |

#### 1. Port 4 Data Direction Register (P4DDR)—H'FF85

| Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|---------------|--------|--------|--------|--------|--------|--------|--------|--------|

|               | P47DDR | P46DDR | P45DDR | P44DDR | P43DDR | P42DDR | P41DDR | P40DDR |

| Initial value | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| Read/Write    | W      | W      | W      | W      | W      | W      | W      | W      |

P4DDR is an 8-bit register that selects the direction of each pin in port 4.

**Single-Chip Mode:** A pin functions as an output pin if the corresponding bit in P4DDR is set to "1," and as in input pin if the bit is cleared to "0."

P4DDR can be written but not read. An attempt to read this register does not cause an error, but all bits are read as "1," regardless of their true values.

At a reset and in the hardware standby mode, P4DDR is initialized to H'00, making all eight pins input pins. P4DDR is not initialized in the software standby mode, so if a P4DDR bit is set to "1" when the chip enters the software standby mode, the corresponding pin continues to output the value in the port 4 data register.

**Expanded Modes:** All bits of P4DDR are fixed at "1" and cannot be modified.

#### 2. Port 4 Data Register (P4DR)-H'FF87

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|

|               | P47 | P46 | P45 | P44 | P43 | P42 | P41 | P40 |

| Initial value | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| Read/Write    | R/W |

P4DR is an 8-bit register containing the data for pins P47 to P40.

At a reset and in the hardware standby mode, P4DR is initialized to H'00.

When the CPU reads P4DR, for output pins it reads the value in the P4DR latch, but for input pins, it obtains the pin status directly.

#### 9.5.3 Pin Functions in Each Mode

Port 4 has different functions in the expanded modes (modes 1, 2, 3, 4) and the single-chip mode (mode 7). Separate descriptions are given below.

**Pin Functions in Expanded Modes:** In the expanded modes (modes 1, 2, 3, and 4), port 4 is used for output of the low bits (A7 - A0) of the address bus. P4DDR is automatically set for output. Figure 9-9 shows the pin functions for the expanded modes.

Figure 9-9 Port 4 Pin Functions in Expanded Modes

**Pin Functions in Single-Chip Mode:** In the single-chip mode (mode 7), each of the port 4 pins can be designated as an input pin or an output pin, as indicated in figure 9-10, by setting the corresponding bit in P4DDR to "1" for output or clearing it to "0" for input.

Figure 9-10 Port 4 Pin Functions in Single-Chip Mode

## 9.6 Port 5

#### 9.6.1 Overview

Port 5 is an 8-bit input/output port with the pin configuration shown in figure 9-11. In the expanded modes that use the on-chip ROM (modes 2 and 4), the pins of port 5 function either as general-purpose input pins or as bits A15 – A8 of the address bus, depending on the port 5 data direction register (P5DDR).

Port 5 has built-in MOS pull-ups that can be turned on or off under program control.

Outputs from port 5 can drive one TTL load and a 90pF capacitive load. They can also drive a Darlington transistor pair.

|                 | Pin                           | Modes 1 and 3 | Modes 2 and 4              | Single-Chip Mode   |

|-----------------|-------------------------------|---------------|----------------------------|--------------------|

| $\rightarrow$   | <ul> <li>P57 / A15</li> </ul> | A15 (output)  | P57 (input) / A15 (output) | P57 (input/output) |

| $ \rightarrow $ | <ul> <li>P56 / A14</li> </ul> | A14 (output)  | P56 (input) / A14 (output) | P56 (input/output) |

| $\checkmark$    | <ul> <li>P55 / A13</li> </ul> | A13 (output)  | P55 (input) / A13 (output) | P55 (input/output) |

| Port -          | <ul> <li>P54 / A12</li> </ul> | A12 (output)  | P54 (input) / A12 (output) | P54 (input/output) |

| 5 🔸             | <ul> <li>P53 / A11</li> </ul> | A11 (output)  | P53 (input) / A11 (output) | P53 (input/output) |

| $\checkmark$    | P52 / A10                     | A10 (output)  | P52 (input) / A10 (output) | P52 (input/output) |

| $ \rightarrow $ | <ul> <li>P51 / A9</li> </ul>  | A9 (output)   | P51 (input) / A9 (output)  | P51 (input/output) |

| $ \rightarrow $ | <ul> <li>P50 / A8</li> </ul>  | A8 (output)   | P50 (input) / A8 (output)  | P50 (input/output) |

Figure 9-11 Pin Functions of Port 5

#### 9.6.2 Port 5 Registers

Register Configuration: Table 9-8 lists the registers of port 5.

| Table 9-8 | Port 5 | Registers |

|-----------|--------|-----------|

|-----------|--------|-----------|

| Name                           | Abbreviation | Read/Write | Initial Value | Address |

|--------------------------------|--------------|------------|---------------|---------|

| Port 5 data direction register | P5DDR        | W          | H'00          | H'FF88  |

| Port 5 data register           | P5DR         | R/W        | H'00          | H'FF8A  |

#### 1. Port 5 Data Direction Register (P5DDR)—H'FF88

| Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|---------------|--------|--------|--------|--------|--------|--------|--------|--------|

|               | P57DDR | P56DDR | P5₅DDR | P54DDR | P53DDR | P52DDR | P51DDR | P50DDR |

| Initial value | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| Read/Write    | W      | W      | W      | W      | W      | W      | W      | W      |

P5DDR is an 8-bit register that selects the direction of each pin in port 5.

**Single-Chip Mode:** A pin functions as an output pin if the corresponding bit in P5DDR is set to "1," and as an input pin if the bit is cleared to "0."

P5DDR can be written but not read. An attempt to read this register does not cause an error, but all bits are read as "1," regardless of their true values.

At a reset and in the hardware standby mode, P5DDR is initialized to H'00, making all eight pins input pins. P5DDR is not initialized in the software standby mode, so if a P5DDR bit is set to "1" when the chip enters the software standby mode, the corresponding pin continues to output the value in the port 5 data register.

**Expanded Modes Using On-Chip ROM (Modes 2 and 4):** If a "1" is set in P5DDR, the corresponding pin is used for address output. If a "0" is set in P5DDR, the pin is used for general-purpose input. P5DDR is initialized to H'00 at a reset and in the hardware standby mode.

**Expanded Modes Not Using On-Chip ROM (Modes 1 and 3):** All bits of P5DDR are fixed at "1" and cannot be modified.

#### Port 5 Data Register (P5DR)-H'FF8A

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|

|               | P57 | P56 | P55 | P54 | P53 | P52 | P51 | P50 |

| Initial value | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| Read/Write    | R/W |

P5DR is an 8-bit register containing the data for pins P57 to P50.

At a reset and in the hardware standby mode, P5DR is initialized to H'00.

When the CPU reads P5DR, for output pins it reads the value in the P5DR latch, but for input pins, it obtains the pin status directly.

#### 9.6.3 Pin Functions in Each Mode

Port 5 operates in one way in modes 1 and 3, in another way in modes 2 and 4, and in a third way in mode 7. Separate descriptions are given below.

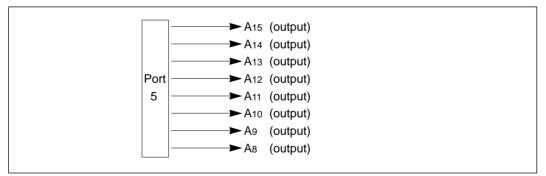

**Pin Functions in Modes 1 and 3:** In modes 1 and 3 (expanded modes in which the on-chip ROM is not used), all bits of P5DDR are automatically set to "1" for output, and the pins of port 5 carry bits A15 – A8 of the address bus. Figure 9-12 shows the pin functions for modes 1 and 3.

Figure 9-12 Port 5 Pin Functions in Modes 1 and 3

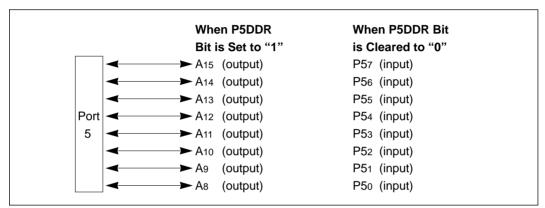

**Pin Functions in Modes 2 and 4:** In modes 2 and 4, (expanded modes in which the on-chip ROM is used), software can select whether to use port 5 for general-purpose input, or for output of bits  $A_{15} - A_8$  of the address bus.

If a bit in P5DDR is set to "1," the corresponding pin is used for address output. If the bit is cleared to "0," the pin is used for input. A reset clears all P5DDR bits to "0," so before the address bus is used, all necessary bits in P5DDR must be set to "1."

Figure 9-13 shows the pin functions in modes 2 and 4.

Figure 9-13 Port 5 Pin Functions in Modes 2 and 4

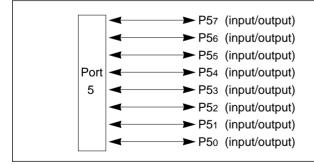

**Pin Functions in Single-Chip Mode:** In the single-chip mode (mode 7), each of the port 5 pins can be designated as an input pin or an output pin, as indicated in figure 9-14, by setting the corresponding bit in P5DDR to "1" for output or clearing it to "0" for input.

Figure 9-14 Port 5 Pin Functions in Single-Chip Mode

#### 9.6.4 Built-In MOS Pull-Up

The MOS input pull-ups of port 5 are turned on by clearing the corresponding bit in P5DDR to "0" and writing a "1" in P5DR. These pull-ups are turned off at a reset and in the hardware standby mode. Table 9-9 indicates the status of the MOS pull-ups in various modes.

#### Table 9-9 Status of MOS Pull-Ups for Port 5

| Mode | Reset | Hardware Standby Mode | Other Operating States* |

|------|-------|-----------------------|-------------------------|

| 1    | OFF   | OFF                   | OFF                     |

| 2    |       |                       | ON/OFF                  |

| 3    |       |                       | OFF                     |

| 4    |       |                       | ON/OFF                  |

| 7    |       |                       |                         |

\* Including the software standby mode.

#### Notation:

| OFF:    | The MOS pull-up is always off.                                             |

|---------|----------------------------------------------------------------------------|

| ON/OFF: | The MOS pull-up is on when $P5DDR = 0$ and $P5DR = 1$ , and off otherwise. |

#### Note on Usage of MOS Pull-Ups

If the bit manipulation instructions listed below are executed on input/output ports 5 and 6 which have selectable MOS pull-ups, the logic levels at input pins will be transferred to the DR latches, causing the MOS pull-ups to be unintentionally switched on or off.

This can occur with the following bit manipulation instructions: BSET, BCLR, BNOT

Specific Example (BSET Instruction): An example will be shown in which the BSET instruction is executed for port 5 under the following conditions:

P57: Input pin, low, MOS pull-up transistor on

P56: Input pin, high, MOS pull-up transistor off

P55 – P50: Output pins, low

The intended purpose of this BSET instruction is to switch the output level at P50 from low to high.

#### A: Before Execution of BSET Instruction

|              | P5 <sub>7</sub> | P5 <sub>6</sub> | P5 <sub>5</sub> | P5 <sub>4</sub> | P5 <sub>3</sub> | P5 <sub>2</sub> | P5 <sub>1</sub> | P5 <sub>0</sub> |

|--------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| Input/output | Input           | Input           | Output          | Output          | Output          | Output          | Output          | Output          |

| Pin state    | Low             | High            | Low             | Low             | Low             | Low             | Low             | Low             |

| DDR          | 0               | 0               | 1               | 1               | 1               | 1               | 1               | 1               |

| DR           | 1               | 0               | 0               | 0               | 0               | 0               | 0               | 0               |

| Pull-up      | On              | Off             |

#### B: Execution of BSET Instruction

BSET.B #0 @PORT5

;set bit 0 in data register

#### C: After Execution of BSET Instruction

|              | P5 <sub>7</sub> | P5 <sub>6</sub> | P5 <sub>5</sub> | P5 <sub>4</sub> | P5 <sub>3</sub> | P5 <sub>2</sub> | P5 <sub>1</sub> | P5 <sub>0</sub> |

|--------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| Input/output | Input           | Input           | Output          | Output          | Output          | Output          | Output          | Output          |

| Pin state    | Low             | High            | Low             | Low             | Low             | Low             | Low             | High            |

| DDR          | 0               | 0               | 1               | 1               | 1               | 1               | 1               | 1               |

| DR           | 0               | 1               | 0               | 0               | 0               | 0               | 0               | 1               |

| Pull-up      | Off             | On              | Off             | Off             | Off             | Off             | Off             | Off             |

**Explanation:** To execute the BSET instruction, the CPU begins by reading port 5. Since P57 and P56 are input pins, the CPU reads the level of these pins directly, not the value in the data register. It reads P57 as low (0) and P56 as high (1).

Since P55 to P50 are output pins, for these pins the CPU reads the value in the data register (0). The CPU therefore reads the value of port 5 as H'40, although the actual value in P5DR is H'80.

Next the CPU sets bit 0 of the read data to 1, changing the value to H'41.

Finally, the CPU writes this value (H'41) back to P5DR to complete the BSET instruction.

As a result, bit P50 is set to 1, switching pin P50 to high output. In addition, bits P57 and P56 are both modified, changing the on/off settings of the MOS pull-up transistors of pins P57 and P56.

**Programming Solution:** The switching of the pull-ups for P57 and P56 in the preceding example can be avoided by using a byte in RAM as a work area for P5DR, performing bit manipulations on the work area, then writing the result to P5DR.

#### A: Before Execution of BSET Instruction

| MOV.B | #80, | R0     |  |

|-------|------|--------|--|

| MOV.B | R0,  | @RAM0  |  |

| MOV.B | R0,  | @PORT5 |  |

;write data (H'80) for data register ;write to work area (RAM0) :write to P5DR

|              | P5 <sub>7</sub> | P5 <sub>6</sub> | P5 <sub>5</sub> | P5 <sub>4</sub> | P5 <sub>3</sub> | P5 <sub>2</sub> | P5 <sub>1</sub> | P5 <sub>0</sub> |

|--------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| Input/output | Input           | Input           | Output          | Output          | Output          | Output          | Output          | Output          |

| Pin state    | Low             | High            | Low             | Low             | Low             | Low             | Low             | Low             |

| DDR          | 0               | 0               | 1               | 1               | 1               | 1               | 1               | 1               |

| DR           | 1               | 0               | 0               | 0               | 0               | 0               | 0               | 0               |

| Pull-up      | On              | Off             |

| RAM0         | 1               | 0               | 0               | 0               | 0               | 0               | 0               | 0               |

#### B: Execution of BSET Instruction

BSET.B #0, @RAM0

;set bit 0 in work area (RAM0)

#### C: After Execution of BSET Instruction

MOV.B @RAM0, R0 MOV.B R0, @PORT5 ;get value in work area (RAM0) ;write value to P5DR

|              | P5 <sub>7</sub> | P5 <sub>6</sub> | P5 <sub>5</sub> | P5 <sub>4</sub> | P5 <sub>3</sub> | P5 <sub>2</sub> | P5 <sub>1</sub> | P5 <sub>0</sub> |

|--------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| Input/output | Input           | Input           | Output          | Output          | Output          | Output          | Output          | Output          |

| Pin state    | Low             | High            | Low             | Low             | Low             | Low             | Low             | High            |

| DDR          | 0               | 0               | 1               | 1               | 1               | 1               | 1               | 1               |

| DR           | 1               | 0               | 0               | 0               | 0               | 0               | 0               | 1               |

| Pull-up      | On              | Off             |

| RAM0         | 1               | 0               | 0               | 0               | 0               | 0               | 0               | 0               |

## 9.7 Port 6

#### 9.7.1 Overview

Port 6 is a 4-bit input/output port with the pin configuration shown in figure 9-15. In mode 4 (the expanded maximum mode that uses the on-chip ROM), the pins of port 6 function either as general-purpose input pins or as the page address bus, depending on the port 6 data direction register (P6DDR).

Port 6 has built-in MOS pull-ups that can be turned on or off under program control.

Outputs from port 6 can drive one TTL load and a 90pF capacitive load. They can also drive a Darlington transistor pair.

|          | Pin       | Mode 3       | Mode 4                     | Mode 1 and 2 and<br>Single-Chip Mode |

|----------|-----------|--------------|----------------------------|--------------------------------------|

|          | P63 / A19 | A19 (output) | P63 (input) / A19 (output) | P63 (input/output)                   |

| Port -   | P62 / A18 | A18 (output) | P62 (input) / A18 (output) | P62 (input/output)                   |

| 6 🔸      | P61 / A17 | A17 (output) | P61 (input) / A17 (output) | P61 (input/output)                   |

| <b>~</b> | P60 / A16 | A16 (output) | P60 (input) / A16 (output) | P60 (input/output)                   |

## Figure 9-15 Pin Functions of Port 6

#### 9.7.2 Port 6 Registers

Register Configuration: Table 9-10 lists the registers of port 6.

#### Table 9-10 Port 6 Registers

| Name                           | Abbreviation | <b>Read/Write</b> | Initial Value | Address |

|--------------------------------|--------------|-------------------|---------------|---------|

| Port 6 data direction register | P6DDR        | W                 | H'F0          | H'FF89  |

| Port 6 data register           | P6DR         | R/W               | H'F0          | H'FF8B  |

#### 1. Port 6 Data Direction Register (P6DDR)—H'FF89

| Bit           | 7 | 6 | 5 | 4 | 3      | 2      | 1      | 0      |

|---------------|---|---|---|---|--------|--------|--------|--------|

|               | — | — | — | — | P63DDR | P62DDR | P61DDR | P60DDR |

| Initial value | 1 | 1 | 1 | 1 | 0      | 0      | 0      | 0      |

| Read/Write    | — | — | — |   | W      | W      | W      | W      |

P6DDR is an 8-bit register that selects the direction of each pin in port 6.

**Single-Chip Mode and Expanded Minimum Modes:** A pin functions as an output pin if the corresponding bit in P6DDR is set to "1," and as an input pin if the bit is cleared to "0."

Bits 3 to 0 can be written but not read. An attempt to read these bits does not cause an error, but all bits are read as "1," regardless of their true values.

Bits 7 to 4 are reserved. They cannot be modified and are always read as "1."

At a reset and in the hardware standby mode, P6DDR is initialized to H'F0, making all four pins input pins. P6DDR is not initialized in the software standby mode, so in the single-chip mode, or expanded minimum mode, if a P6DDR bit is set to "1" when the chip enters the software standby mode, the corresponding pin continues to output the value in the port 6 data register.

**Expanded Maximum Mode Using On-Chip ROM (Mode 4):** If a "1" is set in P6DDR, the corresponding pin is used for address output. If a "0" is set in P6DDR, the pin is used for input. P6DDR is initialized to H'F0 at a reset and in the hardware standby mode.

**Expanded Maximum Mode Not Using On-Chip ROM (Mode 3):** All bits of P6DDR are fixed at "1" and cannot be modified.

#### 2. Port 6 Data Register (P6DR)—H'FF8B

| Bit           | 7 | 6 | 5 | 4 | 3   | 2   | 1   | 0   |

|---------------|---|---|---|---|-----|-----|-----|-----|

|               | — | — |   | _ | P63 | P62 | P61 | P60 |

| Initial value | 1 | 1 | 1 | 1 | 0   | 0   | 0   | 0   |

| Read/Write    | — | _ | — | — | R/W | R/W | R/W | R/W |

P6DR is an 8-bit register containing the data for pins P63 to P60.

Bits 7 to 4 are reserved. They cannot be modified and are always read as "1."

At a reset and in the hardware standby mode, P6DR is initialized to H'F0.

When the CPU reads P6DR, for output pins it reads the value in the P6DR latch, but for input pins, it obtains the pin status directly.

#### 9.7.3 Pin Functions in Each Mode

The usage of port 6 depends on the MCU operating mode. Separate descriptions are given below.

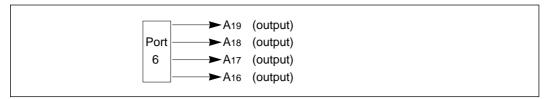

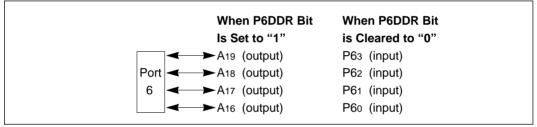

**Pin Functions in Mode 3:** In mode 3 (the expanded maximum mode in which the on-chip ROM is not used), P6DDR is automatically set for output, and the pins of port 6 carry the page address bits  $(A_{19} - A_{16})$  of the address bus. Figure 9-16 shows the pin functions for mode 3.

Figure 9-16 Port 6 Pin Functions in Mode 3

**Pin Functions in Mode 4:** In mode 4, (the expanded maximum mode in which the on-chip ROM is used), software can select whether to use port 6 for general-purpose input, or for output of the page address bits.

If a bit in P6DDR is set to "1," the corresponding pin is used for page address output. If the bit is cleared to "0," the pin is used for input. A reset initializes these pins to the general-purpose input function, so when the address bus is used, all necessary bits in P6DDR must first be set to "1."

Figure 9-17 shows the pin functions in mode 4.

Figure 9-17 Port 6 Pin Functions in Mode 4

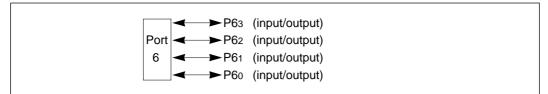

**Pin Functions in Single-Chip Mode and Expanded Minimum Modes:** In the single-chip mode (mode 7) and expanded minimum modes (modes 1 and 2), each of the port 6 pins can be designated as an input pin or an output pin, as indicated in figure 9-18, by setting the corresponding bit in P6DDR to "1" for output or clearing it to "0" for input.

Figure 9-18 Port 6 Pin Functions in Modes 7, 2, and 1

## 9.7.4 Built-in MOS Pull-Up

Port 6 has programmable MOS input pull-ups which are turned on by clearing the corresponding bit in P6DDR to "0" and writing a "1" in P6DR. These pull-ups are turned off at a reset and in the hardware standby mode. Table 9-11 indicates the status of the MOS pull-ups in various modes.

#### Table 9-11 Status of MOS Pull-Ups for Port 5

| Mode | Reset | Hardware Standby Mode | Other Operating States* |

|------|-------|-----------------------|-------------------------|

| 1    | OFF   | OFF                   | ON/OFF                  |

| 2    |       |                       | ON/OFF                  |

| 3    |       |                       | OFF                     |

| 4    |       |                       |                         |

| 7    |       |                       | ON/OFF                  |

|      |       |                       |                         |

\* Including the software standby mode.

#### Notation:

OFF: The MOS pull-up is always off. ON/OFF: The MOS pull-up is on when P6DDR = 0 and P6DR = 1, and off otherwise.

**Note:** When using the built-in pull-ups, see the "Note on Usage of MOS Pull-Ups" in section 9.6.4.

## 9.8 Port 7

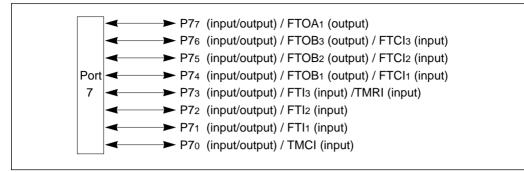

#### 9.8.1 Overview

Port 7 is an 8-bit input/output port with the pin configuration shown in figure 9-19. Its pins also carry input and output signals for the on-chip free-running timers (FRT1, FRT2, and FRT3), and two input signals for the on-chip 8-bit timer.

Port 7 has Schmitt inputs. Outputs from port 7 can drive one TTL load and a 30pF capacitive load. They can also drive a Darlington transistor pair.

Figure 9-19 Pin Functions of Port 7

#### 9.8.2 Port 7 Registers

Register Configuration: Table 9-12 lists the registers of port 7.

#### Table 9-12 Port 7 Registers

| Name                           | Abbreviation | Read/Write | Initial Value | Address |

|--------------------------------|--------------|------------|---------------|---------|

| Port 7 data direction register | P7DDR        | W          | H'00          | H'FF8C  |

| Port 7 data register           | P7DR         | R/W        | H'00          | H'FF8E  |

#### 1. Port 7 Data Direction Register (P7DDR)—H'FF8C

| Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|---------------|--------|--------|--------|--------|--------|--------|--------|--------|

|               | P77DDR | P76DDR | P7₅DDR | P74DDR | P73DDR | P72DDR | P71DDR | P7₀DDR |

| Initial value | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| Read/Write    | W      | W      | W      | W      | W      | W      | W      | W      |

P7DDR is an 8-bit register that selects the direction of each pin in port 7. A pin functions as an output pin if the corresponding bit in P7DDR is set to "1," and as an input pin if the bit is cleared to "0."

P7DDR can be written but not read. An attempt to read this register does not cause an error, but all bits are read as "1," regardless of their true values.

At a reset and in the hardware standby mode, P7DDR is initialized to H'00, setting all pins for input. P7DDR is not initialized in the software standby mode, so if a P7DDR bit is set to "1" when the chip enters the software standby mode, the corresponding pin continues to output the value in the port 7 data register.

A transition to the software standby mode initializes the on-chip supporting modules, so any pins of port 7 that were being used by an on-chip timer when the transition occurs revert to general-purpose input or output, controlled by P7DDR and P7DR.

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|

|               | P77 | P76 | P75 | P74 | P73 | P72 | P71 | P70 |

| Initial value | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| Read/Write    | R/W |

## 2. Port 7 Data Register (P7DR)—H'FF8E

P7DR is an 8-bit register containing the data for pins P77 to P70. When the CPU reads P7DR, for output pins it reads the value in the P7DR latch, but for input pins, it obtains the pin status directly.

## 9.8.3 Pin Functions

The pin functions of port 7 are the same in all MCU operating modes. As figure 9-19 indicated, these pins are used for input and output of on-chip timer signals as well as for general-purpose input and output. For some pins, two or more functions can be enabled simultaneously.

P77 can be used either for general-purpose input/output, or as the output pin for the output compare A signal (FTOA) from free-running timer 1.

P76 to P74 can be used either for general-purpose input/output, or as the output pins for the output compare B signals (FTOB) from free-running timers 3 to 1. When used for general-purpose input and output, they can also provide external clock input (FTCI) to the free-running counters. This additional function is selected when the clock select 1 and 0 bits (CKS1 and CKS0) in the free-running timer control registers are both set to "1."

P73 to P71 function simultaneously as general-purpose input/output pins and as input pins for the input capture signals (FTI) of free-running timers 3 to 1.

P73 and P70 can be used for timer reset input (TMRI) and timer clock input (TMCI) for the 8-bit timer, as well as for general-purpose input and output.

Table 9-13 shows how the functions of the pins of port 7 are selected.

| Table 9-13         Port 7 Pin Functions |

|-----------------------------------------|

|-----------------------------------------|

| Pin                 | Selection of Pin Functions |                                                                                  |                |                |               |                 |  |  |  |

|---------------------|----------------------------|----------------------------------------------------------------------------------|----------------|----------------|---------------|-----------------|--|--|--|

| P77 /               | The function               | depends on th                                                                    | he output enab | ole A bit (OEA | ) of the FRT1 | timer control   |  |  |  |

| FTOA1               | register (TCF              | R) and on the                                                                    | P77DDR bit as  | s follows:     |               |                 |  |  |  |

|                     |                            |                                                                                  |                |                |               |                 |  |  |  |

|                     | OEA                        | 0                                                                                |                |                | 1             |                 |  |  |  |

|                     | P77DDR                     | 0 1                                                                              |                | 0              | 1             |                 |  |  |  |

|                     | Pin function               | P77 input                                                                        | P77 output     | FTOA1          | output        | -               |  |  |  |

|                     |                            | •                                                                                |                |                | •             | ]               |  |  |  |

| P76/                | The function               | The function depends on the output compare B bit (OEB) of the FRT3 timer control |                |                |               |                 |  |  |  |

| FTOB3 /             |                            | •                                                                                | P76DDR bit as  | • •            | ,             |                 |  |  |  |

| FTCI3               | . eg.etet (                | .,                                                                               |                |                |               |                 |  |  |  |

|                     | OEB                        | 0                                                                                |                | -              | 1             | 1               |  |  |  |

|                     | P76DDR                     |                                                                                  |                | 1              | -             |                 |  |  |  |

|                     | Pin function               | P76 input                                                                        | P76 output     | FTOB3 output   |               | -               |  |  |  |

|                     |                            | FTCl3                                                                            |                | 11000          |               |                 |  |  |  |

|                     |                            | 11013                                                                            | input          |                |               | ]               |  |  |  |

| P75 /               | The function               | depends on th                                                                    | he output com  | pare B bit (OE | B) of the FRT | 2 timer control |  |  |  |

| FTOB <sub>2</sub> / |                            | •                                                                                | P75DDR bit as  | • •            | ,             |                 |  |  |  |

| FTCl <sub>2</sub>   |                            | ,                                                                                |                |                |               |                 |  |  |  |

| 1 1 012             | OEB                        | 0                                                                                |                |                | 1             | 1               |  |  |  |

|                     | P75DDR                     | 0                                                                                | 1              | 0              | 1             | -               |  |  |  |

|                     | Pin function               | P75 input                                                                        | P75 output     | -              | •             | -               |  |  |  |

|                     | FILLINGTON                 | •                                                                                |                | FTOB2          |               |                 |  |  |  |

|                     |                            | FTCl2                                                                            | input          |                |               | ]               |  |  |  |

| P74 /               | The function               | dananda an ti                                                                    |                | nora D hit (OF |               | 1 timer central |  |  |  |

|                     |                            | •                                                                                | •              | • •            |               | 1 timer control |  |  |  |

| FTOB1 /             | register (1CF              | () and on the                                                                    | P74DDR bit as  | s follows:     |               |                 |  |  |  |

| FTCI1               |                            |                                                                                  |                |                |               | -               |  |  |  |

|                     | OEB                        | 0                                                                                |                | -              | 1             | _               |  |  |  |

|                     | P74DDR                     | 0                                                                                | 1              | 0              | 1             |                 |  |  |  |

|                     | Pin function               | P74 input                                                                        | P74 output     | FTOB1          | output        |                 |  |  |  |

|                     |                            | FTCI1                                                                            | input          |                |               |                 |  |  |  |

|                     | L                          |                                                                                  |                |                | J             |                 |  |  |  |

#### Table 9-13 Port 7 Pin Functions (cont)

# Pin Selection of Pin Functions P73 / FTI3 / The function depends on the counter clear bits 1 and 0 (CCLR1 and CCLR0) in the timer control register (TCR) of the 8-bit timer, and on the P73DDR bit as follows:

CCLR1, CCLR0: At least one bit is "0." Both bits are set to "1"

| P73DDR       | 0                         | 1          |  |  |  |

|--------------|---------------------------|------------|--|--|--|

| Pin function | P73 input                 | P73 output |  |  |  |

|              | FTI3 input and TMRI input |            |  |  |  |

#### P72 / FTI2

| P72DDR       | 0          | 1          |  |  |  |

|--------------|------------|------------|--|--|--|

| Pin function | P72 input  | P72 output |  |  |  |

|              | FTI2 input |            |  |  |  |

#### P71 / FTI1

| P71DDR       | 0          | 1          |  |  |  |

|--------------|------------|------------|--|--|--|

| Pin function | P71 input  | P71 output |  |  |  |

|              | FTI1 input |            |  |  |  |

P70 / TMCI This pin always has a general-purpose input/output function, and can simultaneously be used for external clock input for the 8-bit timer, depending on clock select bits 2 to 0 (CKS2, CKS1, and CKS0) in the timer control register (TCR). See section 11, "8-bit Timer" for details.

| P70DDR       | 0          | 1          |  |  |  |

|--------------|------------|------------|--|--|--|

| Pin function | P70 input  | P70 output |  |  |  |

|              | TMCI input |            |  |  |  |

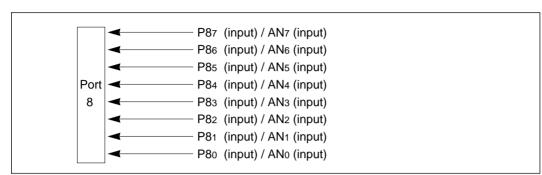

## 9.9 Port 8

#### 9.9.1 Overview

Port 8 is an 8-bit input port that also receives inputs for the on-chip A/D converter. The pin functions are the same in all MCU operating modes, as shown in figure 9-20.

Figure 9-20 Pin Functions of Port 8

#### 9.9.2 Port 8 Registers

**Register Configuration:** Port 8 has only the data register described in table 9-14. Since it is exclusively an input port, there is no data direction register.

#### Table 9-14 Port 8 Registers

| Name                 | Abbreviation | Read/Write | Address |

|----------------------|--------------|------------|---------|

| Port 8 data register | P8DR         | R          | H'FF8F  |

#### 1. Port 8 Data Register (P8DR)—H'FF8F

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|

|               | P87 | P86 | P85 | P84 | P83 | P82 | P81 | P80 |

| Initial value | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| Read/Write    | R   | R   | R   | R   | R   | R   | R   | R   |

When the CPU reads P8DR it always reads the current status of each pin, except that during A/D conversion the pin currently being converted reads "1" regardless of the actual input voltage at that pin.

## 9.10 Port 9

## 9.10.1 Overview

Port 9 is an 8-bit input/output port with the pin configuration shown in figure 9-21. In addition to general-purpose input and output, its pins are used for the output compare A signals from free-running timers 2 and 3, for PWM timer output, and for input and output by the on-chip serial communication interface 9 (SCI). The pin functions are the same in all MCU operating modes.

Outputs from port 9 can drive one TTL load and a 30pF capacitive load. They can also drive a Darlington transistor pair.

Figure 9-21 Pin Functions of Port 9

#### 9.10.2 Port 9 Registers

**Register Configuration:** Table 9-15 lists the registers of port 9.

#### Table 9-15 Port 9 Registers

| Name                           | Abbreviation | Read/Write | Initial Value | Address |

|--------------------------------|--------------|------------|---------------|---------|

| Port 9 data direction register | P9DDR        | W          | H'00          | H'FFFE  |

| Port 9 data register           | P9DR         | R/W        | H'00          | H'FFFF  |

#### 1. Port 9 Data Direction Register (P9DDR)—H'FFFE

| Bit           | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|---------------|--------|--------|--------|--------|--------|--------|--------|--------|

|               | P97DDR | P96DDR | P95DDR | P94DDR | P93DDR | P92DDR | P91DDR | P90DDR |

| Initial value | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| Read/Write    | W      | W      | W      | W      | W      | W      | W      | W      |

P9DDR is an 8-bit register that selects the direction of each pin in port 9. A pin functions as an output pin if the corresponding bit in P9DDR is set to "1," and as an input pin if the bit is cleared to "0."

P9DDR can be written but not read. An attempt to read this register does not cause an error, but all bits are read as "1," regardless of their true values.

At a reset and in the hardware standby mode, P9DDR is initialized to H'00, setting all pins for input. P9DDR is not initialized in the software standby mode, so if a P9DDR bit is set to "1" when the chip enters the software standby mode, the corresponding pin continues to output the value in the port 9 data register.

A transition to the software standby mode initializes the on-chip supporting modules, so any pins of port 9 that were being used by an on-chip module (example: free-running timer output) when the transition occurs revert to general-purpose input or output, controlled by P9DDR and P9DR.

#### 2. Port 9 Data Register (P9DR)—H'FFFF

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|

|               | P97 | P96 | P95 | P94 | P93 | P92 | P91 | P90 |

| Initial value | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| Read/Write    | R/W |

P9DR is an 8-bit register containing the data for pins P97 to P90. When the CPU reads P9DR, for output pins it reads the value in the P9DR latch, but for input pins, it obtains the pin status directly.

#### 9.10.3 Pin Functions

The pin functions of port 9 are the same in all MCU operating modes. As figure 9-21 indicated, these pins are used for output of on-chip timer signals and for input and output of serial data and clock signals as well as for general-purpose input and output. Specifically, they carry output signals for free-running timers 2 and 3, output signals for the pulse-width modulation (PWM) timer, and input and output signals for the serial communication interface.

Table 9-16 shows how the functions of the pins of port 9 are selected.

## Table 9-16Port 9 Pin Functions

| Pin   | Selection of Pin Functions                                                                   |

|-------|----------------------------------------------------------------------------------------------|

| P97 / | The function depends on the communication mode bit $(C/\overline{A})$ and the clock enable 1 |

| SCK   | and 2 bits (CKE1 and CKE0) of the serial control register (SCR) of the serial                |

|       | communication interface as follows:                                                          |

| C/Ā          | 0       |          |          | 0 1    |         |       |          |        |

|--------------|---------|----------|----------|--------|---------|-------|----------|--------|

| CKE1         | 0       |          |          | 1      | (       | 0     |          | 1      |

| CKE0         | 0       | 1        | 0        | 1      | 0       | 1     | 0        | 1      |

| Pin function | P97     | SCI      | SCI ext  | ternal | SCI int | ernal | SCI ext  | ternal |

|              | input   | internal | clock ir | nput   | clock o | utput | clock ir | nput   |

|              | or      | clock    |          |        |         |       |          |        |

|              | output* | output   |          |        |         |       |          |        |

\* Input or output is selected by the P97DDR bit.

P96 / RXD The function depends on the receive enable bit (RE) of the serial control register (SCR) and on the P96DDR bit as follows: