# Section 11 8-Bit Timer

#### 11.1 Overview

The H8/532 chip includes a single 8-bit timer based on an 8-bit counter (TCNT). The timer has two time constant registers (TCORA and TCORB) that are constantly compared with the TCNT value to detect compare-match events. One application of the 8-bit timer is to generate a rectangular-wave output with an arbitrary duty factor.

#### 11.1.1 Features

The features of the 8-bit timer are listed below.

- Selection of four clock sources

The counter can be driven by an internal clock signal (ø/8, ø/64, or ø/1024) or an external clock input (enabling use as an external event counter).

- Selection of three ways to clear the counter

The counter can be cleared on compare-match A or B, or by an external reset signal.

- Timer output controlled by two time constants

The single timer output (TMO) is controlled by two independent time constants, enabling the timer to generate output waveforms with an arbitrary duty factor.

- Three types of interrupts

Compare-match A and B and overflow interrupts can be requested independently.

The compare match interrupts can be served by the data transfer controller (DTC), enabling interrupt-driven data transfer with minimal CPU programming.

## 11.1.2 Block Diagram

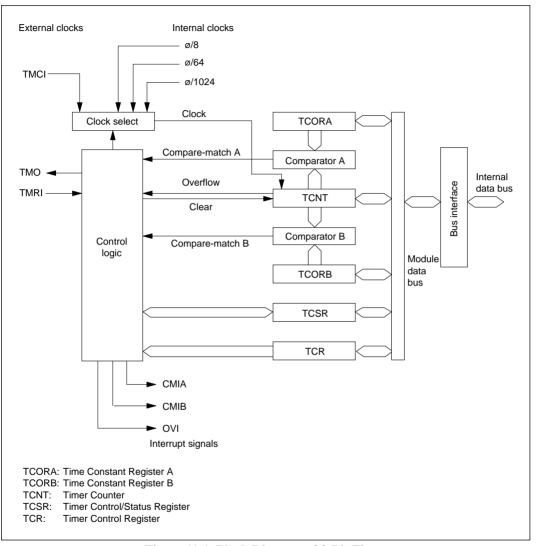

Figure 11-1 shows a block diagram of 8-bit timer.

Figure 11-1 Block Diagram of 8-Bit Timer

## 11.1.3 Input and Output Pins

Table 11-1 lists the input and output pins of the 8-bit timer.

Table 11-1 Input and Output Pins of 8-Bit Timer

| Name              | Abbreviation | I/O    | Function                              |

|-------------------|--------------|--------|---------------------------------------|

| Timer output      | TMO          | Output | Output controlled by compare-match    |

| Timer clock input | TMCI         | Input  | External clock source for the counter |

| Timer reset input | TMRI         | Input  | External reset signal for the counter |

## 11.1.4 Register Configuration

Table 11-2 lists the registers of the 8-bit timer.

**Table 11-2 8-Bit Timer Registers**

| Name                          | Abbreviation | R/W    | Initial Value | Address |

|-------------------------------|--------------|--------|---------------|---------|

| Timer control register        | TCR          | R/W    | H'00          | H'FFD0  |

| Timer control/status register | TCSR         | R/(W)* | H'10          | H'FFD1  |

| Timer constant register A     | TCORA        | R/W    | H'FF          | H'FFD2  |

| Timer constant register B     | TCORB        | R/W    | H'FF          | H'FFD3  |

| Timer counter                 | TCNT         | R/W    | H'00          | H'FFD4  |

<sup>\*</sup> Software can write a "0" to clear bits 7 to 5, but cannot write a "1" in these bits.

# 11.2 Register Descriptions

## 11.2.1 Timer Counter (TCNT)—H'FFD4

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|

|               |     |     |     |     |     |     |     |     |

| Initial value | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| Read/Write    | R/W |

The timer counter (TCNT) is an 8-bit up-counter that increments on a pulse generated from one of four clock sources. The clock source is selected by clock select bits 2 to 0 (CKS2 to CKS0) of the timer control register (TCR). The CPU can always read or write the timer counter.

The timer counter can be cleared by an external reset input or by an internal compare-match signal generated at a compare-match event. Clock clear bits 1 and 0 (CCLR1 and CCLR0) of the timer control register select the method of clearing.

When the timer counter overflows from H'FF to H'00, the overflow flag (OVF) in the timer control/status register (TCSR) is set to "1."

The timer counter is initialized to H'00 at a reset and in the standby modes.

#### 11.2.2 Time Constant Registers A and B (TCORA and TCORB)—H'FFD2 and H'FFD3

| Bit           | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|---------------|-----|-----|-----|-----|-----|-----|-----|-----|

|               |     |     |     |     |     |     |     |     |

| Initial value | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

| Read/Write    | R/W |

TCORA and TCORB are 8-bit readable/writable registers. The timer count is continually compared with the constants written in these registers. When a match is detected, the corresponding compare-match flag (CMFA or CMFB) is set in the timer control/status register (TCSR).

The timer output signal (TMO) is controlled by these compare-match signals as specified by output select bits 1 to 0 (OS1 to OS0) in the timer status/control register (TCSR).

TCORA and TCORB are initialized to H'FF at a reset and in the standby modes.

#### 11.2.3 Timer Control Register (TCR)—H'FFD0

| Bit           | 7     | 6     | 5    | 4     | 3     | 2    | 1    | 0    |

|---------------|-------|-------|------|-------|-------|------|------|------|

|               | CMIEB | CMIEA | OVIE | CCLR1 | CCLR0 | CKS2 | CKS1 | CKS0 |

| Initial value | 0     | 0     | 0    | 0     | 0     | 0    | 0    | 0    |

| Read/Write    | R/W   | R/W   | R/W  | R/W   | R/W   | R/W  | R/W  | R/W  |

The TCR is an 8-bit readable/writable register that selects the clock source and the time at which the timer counter is cleared, and enables interrupts.

The TCR is initialized to H'00 at a reset and in the standby modes.

**Bit 7—Compare-match Interrupt Enable B (CMIEB):** This bit selects whether to request compare-match interrupt B (CMIB) when compare-match flag B (CMFB) in the timer status/control register (TCSR) is set to "1."

| Bit | 7 |

|-----|---|

|-----|---|

| CMIEB | Description                                           |                 |

|-------|-------------------------------------------------------|-----------------|

| 0     | Compare-match interrupt request B (CMIB) is disabled. | (Initial value) |

| 1     | Compare-match interrupt request B (CMIB) is enabled.  |                 |

**Bit 6—Compare-match Interrupt Enable A (CMIEA):** This bit selects whether to request compare-match interrupt A (CMIA) when compare-match flag A (CMFA) in the timer status/control register (TCSR) is set to "1."

#### Bit 6

| <b>CMIEA</b> | Description                                           |                 |

|--------------|-------------------------------------------------------|-----------------|

| 0            | Compare-match interrupt request A (CMIA) is disabled. | (Initial value) |

| 1            | Compare-match interrupt request A (CMIA) is enabled.  |                 |

**Bit 5—Timer Overflow Interrupt Enable (OVIE):** This bit selects whether to request a timer overflow interrupt (OVI) when the overflow flag (OVF) in the timer status/control register (TCSR) is set to "1."

#### Bit 5

| OVIE | Description                                             |                 |

|------|---------------------------------------------------------|-----------------|

| 0    | The timer overflow interrupt request (OVI) is disabled. | (Initial value) |

| 1    | The timer overflow interrupt request (OVI) is enabled.  |                 |

Bits 4 and 3—Counter Clear 1 and 0 (CCLR1 and CCLR0): These bits select how the timer counter is cleared: by compare-match A or B or by an external reset input.

| Bit 4 | Bit 3 |                                    |                     |  |

|-------|-------|------------------------------------|---------------------|--|

| CCLR1 | CCLR0 | Description                        |                     |  |

| 0     | 0     | Not cleared.                       | (Initial value)     |  |

| 0     | 1     | Cleared on compare-match A.        |                     |  |

| 1     | 0     | Cleared on compare-match B.        |                     |  |

| 1     | 1     | Cleared on rising edge of external | reset input signal. |  |

Bits 2, 1, and 0—Clock Select (CKS2, CKS1, and CKS0): These bits select the internal or external clock source for the timer counter. For the external clock source they select whether to increment the count on the rising or falling edge of the clock input, or on both edges.

| Bit 2 | Bit 1 | Bit 0 |                                                     |

|-------|-------|-------|-----------------------------------------------------|

| CKS2  | CKS1  | CKS0  | Description                                         |

| 0     | 0     | 0     | No clock source (timer stopped). (Initial value)    |

| 0     | 0     | 1     | Internal clock source (ø/8).                        |

| 0     | 1     | 0     | Internal clock source (ø/64).                       |

| 0     | 1     | 1     | Internal clock source (ø/1024).                     |

| 1     | 0     | 0     | No clock source (timer stopped).                    |

| 1     | 0     | 1     | External clock source, counted on the rising edge.  |

| 1     | 1     | 0     | External clock source, counted on the falling edge. |

| 1     | 1     | 1     | External clock source, counted on both the rising   |

|       |       |       | and falling edges.                                  |

## 11.2.4 Timer Control/Status Register (TCSR)

| Bit           | 7      | 6      | 5      | 4 | 3   | 2   | 1   | 0   |

|---------------|--------|--------|--------|---|-----|-----|-----|-----|

|               | CMFB   | CMFA   | OVF    | _ | OS3 | OS2 | OS1 | OS0 |

| Initial value | 0      | 0      | 0      | 1 | 0   | 0   | 0   | 0   |

| Read/Write    | R/(W)* | R/(W)* | R/(W)* | _ | R/W | R/W | R/W | R/W |

The TCSR is an 8-bit readable and partially writable\* register that indicates compare-match and overflow status and selects the effect of compare-match events on the timer output signal (TMO).

The TCSR is initialized to H'10 at a reset and in the standby modes.

**Bit 7—Compare-Match Flag B (CMFB):** This status flag is set to "1" when the timer count matches the time constant set in TCORB.

<sup>\*</sup> Software can write a "0" in bits 7 to 5 to clear the flags, but cannot write a "1" in these bits.

| Bit 7 |                                                                               |                 |

|-------|-------------------------------------------------------------------------------|-----------------|

| CMFB  | Description                                                                   |                 |

| 0     | This bit is cleared from 1 to 0 when:                                         | (Initial value) |

|       | 1. The CPU reads the CMFB bit, then writes a "0" in this bit.                 |                 |

|       | 2. Compare-match interrupt B is served by the data transfer controller (DTC). |                 |

| 1     | This hit is set to 1 when TCNT = TCORB                                        |                 |

**Bit 6—Compare-Match Flag A (CMFA):** This status flag is set to "1" when the timer count matches the time constant set in TCORA.

## Bit 6

| CMFA | Description                                                                   |                 |

|------|-------------------------------------------------------------------------------|-----------------|

| 0    | This bit is cleared from 1 to 0 when:                                         | (Initial value) |

|      | 1. The CPU reads the CMFA bit, then writes a "0" in this bit.                 |                 |

|      | 2. Compare-match interrupt A is served by the data transfer controller (DTC). |                 |

| 1    | This bit is set to 1 when TCNT = TCORA.                                       |                 |

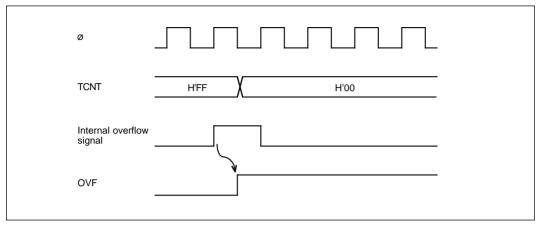

Bit 5—Timer Overflow Flag (OVF): This status flag is set to "1" when the timer count overflows (changes from H'FF to H'00).

#### Bit 5

| OVF | Description                                                        |  |

|-----|--------------------------------------------------------------------|--|

| 0   | This bit is cleared from 1 to 0 when the CPU reads (Initial value) |  |

|     | the OVF bit, then writes a "0" in this bit.                        |  |

| 1   | This bit is set to 1 when TCNT changes from H'FF to H'00.          |  |

**Bit 4—Reserved:** This bit cannot be modified and is always read as "1."

**Bits 3 to 0—Output Select 3 to 0 (OS3 to OS0):** These bits specify the effect of compare-match events on the timer output signal (TMO). Bits OS3 and OS2 control the effect of compare-match B on the output level. Bits OS1 and OS0 control the effect of compare-match A on the output level.

When all four output select bits are cleared to "0" the TMO signal is not output. The TMO output is "0" before the first compare-match.

| Bit 3 | Bit 2 |                                                        |

|-------|-------|--------------------------------------------------------|

| OS3   | OS2   | Description                                            |

| 0     | 0     | No change when compare-match B occurs. (Initial value) |

| 0     | 1     | Output changes to "0" when compare-match B occurs.     |

| 1     | 0     | Output changes to "1" when compare-match B occurs.     |

| 1     | 1     | Output inverts (toggles) when compare-match B occurs.  |

| Bit 1 | Bit 0 |                                                        |  |

|-------|-------|--------------------------------------------------------|--|

| OS1   | OS0   | Description                                            |  |

| 0     | 0     | No change when compare-match A occurs. (Initial value) |  |

| 0     | 1     | Output changes to "0" when compare-match A occurs.     |  |

| 1     | 0     | Output changes to "1" when compare-match A occurs.     |  |

| 1     | 1     | Output inverts (toggles) when compare-match A occurs   |  |

## 11.3 Operation

## 11.3.1 TCNT Incrementation Timing

The timer counter increments on a pulse generated once for each period of the selected (internal or external) clock source.

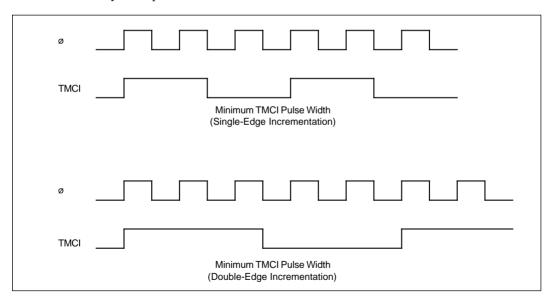

If external clock input (TMCI) is selected, the timer counter can increment on the rising edge, the falling edge, or both edges of the external clock signal.

The external clock pulse width must be at least 1.5-ø clock periods for incrementation on a single edge, and at least 2.5-ø clock periods for incrementation on both edges. The counter will not increment correctly if the pulse width is shorter than these values.

Figure 11-2 Count Timing for External Clock Input

## 11.3.2 Compare Match Timing

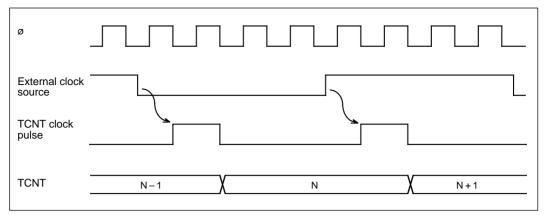

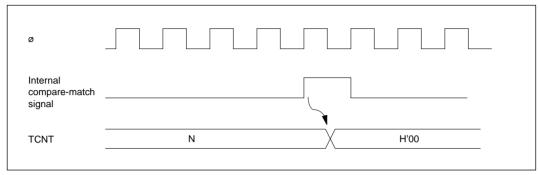

**Setting of Compare-Match Flags A and B (CMFA and CMFB):** The compare-match flags are set to "1" by an internal compare-match signal generated when the timer count matches the time constant in TCORA or TCORB. The compare-match signal is generated at the last state in which the match is true, just before the timer counter increments to a new value.

Accordingly, when the timer count matches one of the time constants, the compare-match signal is not generated until the next period of the clock source. Figure 11-3 shows the timing of the setting of the compare-match flags.

Figure 11-3 Setting of Compare-Match Flags

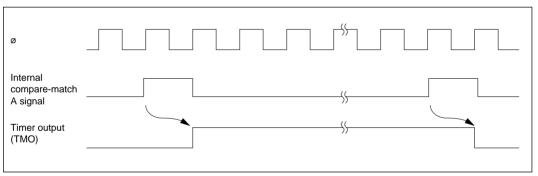

**Output Timing:** When a compare-match event occurs, the timer output (TMO) changes as specified by the output select bits (OS3 to OS0) in the TCSR. Depending on these bits, the output can remain the same, change to "0," change to "1," or toggle.

Figure 11-4 shows the timing when the output is set to toggle on compare-match A.

Figure 11-4 Timing of Timer Output

## **Timing of Compare-Match Clear**

Depending on the CCLR1 and CCLR0 bits in the TCR, the timer counter can be cleared when compare-match A or B occurs. Figure 11-5 shows the timing of this operation.

Figure 11-5 Timing of Compare-Match Clear

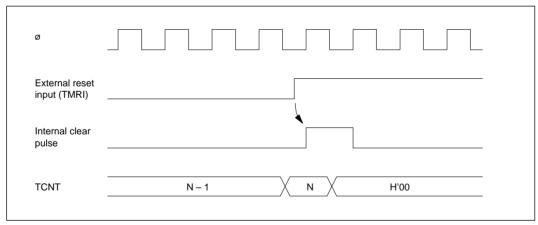

#### 11.3.3 External Reset of TCNT

When the CCLR1 and CCLR0 bits in the TCR are both set to "1," the timer counter is cleared on the rising edge of an external reset input. Figure 11-6 shows the timing of this operation.

Figure 11-6 Timing of External Reset

#### 11.3.4 Setting of TCNT Overflow Flag

The overflow flag (OVF) is set to "1" when the timer count overflows (changes from H'FF to H'00). Figure 11-7 shows the timing of this operation.

Figure 11-7 Setting of Overflow Flag (OVF)

# 11.4 CPU Interrupts and DTC Interrupts

The 8-bit timer can generate three types of interrupts: compare-match A and B (CMIA and CMIB), and overflow (OVI). Each interrupt is requested when the corresponding enable and flag bits are set in the TCR and TCSR. Independent signals are sent to the interrupt controller for each type of interrupt. Table 11-3 lists information about these interrupts.

**Table 11-3 8-Bit Timer Interrupts**

| Interrupt | Description                | DTC Service Available? | Priority |

|-----------|----------------------------|------------------------|----------|

| CMIA      | Requested when CMFA is set | Yes                    | High     |

| CMIB      | Requested when CMFB is set | Yes                    | <b>A</b> |

| OVI       | Requested when OVF is set  | No                     | Low      |

The CMIA and CMIB interrupts can be served by the data transfer controller (DTC) to have a data transfer performed.

When the DTC serves one of these interrupts, it automatically clears the CMFA or CMFB flag to "0." See section 6, "Data Transfer Controller" for further information on the DTC.

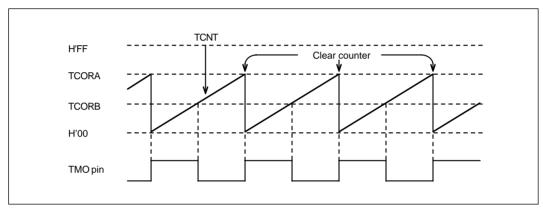

# 11.5 Sample Application

In the example below, the 8-bit timer is used to generate a pulse output with a selected duty factor. The control bits are set as follows:

- 1. In the TCR, CCLR1 is cleared to "0" and CCLR0 is set to "1" so that the timer counter is cleared when its value matches the constant in TCORA.

- 2. In the TCSR, bits OS3 to OS0 are set to "0110," causing the output to change to "1" on compare-match A and to "0" on compare-match B.

With these settings, the 8-bit timer provides output of pulses at a rate determined by TCORA with a pulse width determined by TCORB. No software intervention is required.

Figure 11-8 Example of Pulse Output

# 11.6 Application Notes

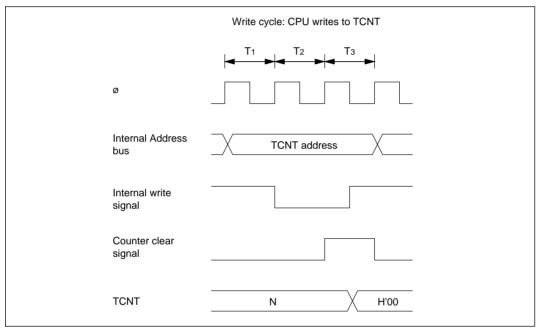

Application programmers should note that the following types of contention can occur in the 8-bit timer.

**Contention between TCNT Write and Clear:** If an internal counter clear signal is generated during the T3 state of a write cycle to the timer counter, the clear signal takes priority and the write is not performed.

Figure 11-9 shows this type of contention.

Figure 11-9 TCNT Write-Clear Contention

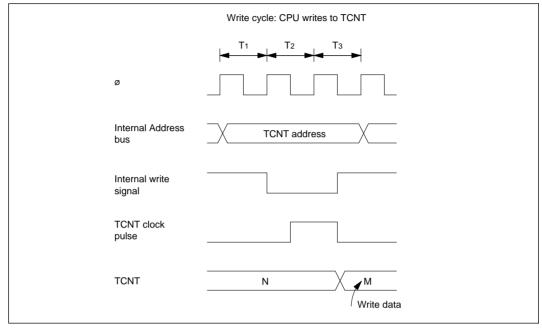

**Contention between TCNT Write and Increment:** If a timer counter increment pulse is generated during the T3 state of a write cycle to the timer counter, the write takes priority and the timer counter is not incremented.

Figure 11-10 shows this type of contention.

Figure 11-10 TCNT Write-Increment Contention

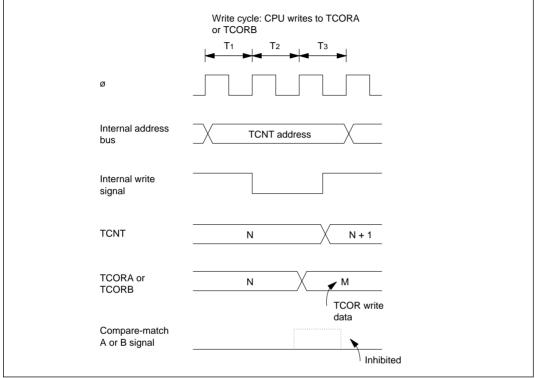

**Contention between TCOR Write and Compare-Match:** If a compare-match occurs during the T3 state of a write cycle to TCORA or TCORB, the write takes precedence and the compare-match signal is inhibited.

Figure 11-11 shows this type of contention.

Figure 11-11 Contention between TCOR Write and Compare-Match

Contention between Compare-Match A and Compare-Match B: If identical time constants are written in TCORA and TCORB, causing compare-match A and B to occur simultaneously, any conflict between the output selections for compare-match A and B is resolved by following the priority order in table 11-4.

Table 11-4 Priority Order of Timer Output

| Output Selection | Priority |

|------------------|----------|

| Toggle           | High     |

| "1" Output       | <b>A</b> |

| "0" Output       |          |

| No change        | Low      |

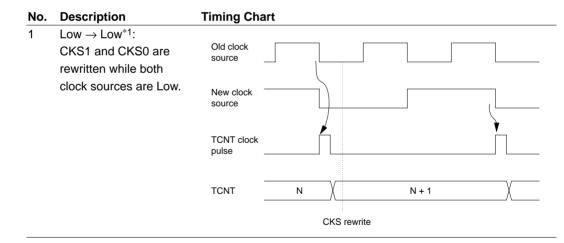

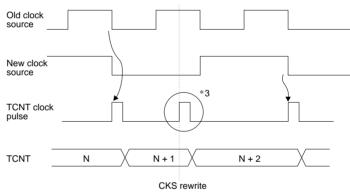

**Incrementation Caused by Changing of Internal Clock Source:** When an internal clock source is changed, the changeover may cause the timer counter to increment. This depends on the time at which the clock select bits (CKS2 to CKS0) are rewritten, as shown in table 11-5.

The pulse that increments the timer counter is generated at the falling edge of the internal clock source signal. If clock sources are changed when the old source is High and the new source is Low, as in case No. 3 in table 11-5, the changeover generates a falling edge that triggers the TCNT clock pulse and increments the timer counter.

Switching between an internal and external clock source can also cause the timer counter to increment

**Table 11-5 Effect of Changing Internal Clock Sources**

**Note:** \*1 Including a transition from Low to the stopped state (CKS1 = 0, CKS0 = 0), or a transition from the stopped state to Low.

**Table 11-5 Effect of Changing Internal Clock Sources (cont)**

#### **Timing Chart Description** No. 2 Low $\rightarrow$ High\*1: Old clock CKS1 and CKS0 are source rewritten while old clock source is Low and New clock new clock source is High. source TCNT clock pulse **TCNT** Ν N + 1N+2CKS rewrite High $\rightarrow$ Low\*2: 3

3 High → Low\*<sup>2</sup>: CKS1 and CKS0 are rewritten while old clock source is High and new clock source is Low.

**Note:** \*1 Including a transition from the stopped state to High.

\*2 Including a transition from High to the stopped state.

\*3 The switching of clock sources is regarded as a falling edge that increments the TCNT.

**Table 11-5 Effect of Changing Internal Clock Sources (cont)**

#### No. Description **Timing Chart** High → High: 4 CKS1 and CKS0 are Old clock source rewritten while both clock sources are High. New clock source TCNT clock pulse **TCNT** Ν N + 1 N + 2CKS rewrite